XADC core is controlled and accessed from a user design via the Dynamic Reconfiguration Port (DRP). The DRP also provides access to voltage monitors that are present on each of the FPGA's power rails, and a temperature sensor that is internal to the FPGA. For more information on using the XADC core, refer to the Xilinx document titled "7 Series FPGAs and Zyng-7000 All Programmable SoC XADC Dual 12-Bit 1 MSPS Analog-to-Digital Converter."

# 12 MicroSD Slot

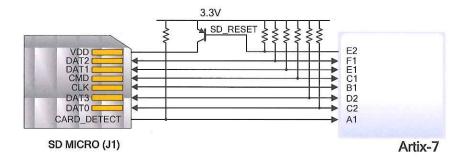

The Nexys4 DDR provides a microSD slot for both FPGA configuration and user access. The on-board Auxiliary Function microcontroller shares the SD card bus with the FPGA. Before the FPGA is configured the microcontroller must have access to the SD card via SPI. Once a bit file is downloaded to the FPGA (from any source), the microcontroller power cycles the SD slot and relinquishes control of the bus. This enables any SD card in the slot to reset its internal state machines and boot up in SD native bus mode. All of the SD pins on the FPGA are wired to support full SD speeds in native interface mode, as shown in Figure 21. The SPI is also available, if needed. Once control over the SD bus is passed from the microcontroller to the FPGA, the SD\_RESET signal needs to be actively driven low by the FPGA to power the microSD card slot. For information on implementing an SD card controller, refer to the SD card specification available at <a href="https://www.sdcard.org">www.sdcard.org</a>.

Figure 21. Artix-7 microSD card connector interface (PIC24 connections not shown).

# 13 Temperature Sensor

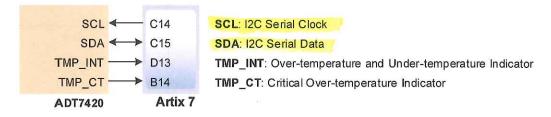

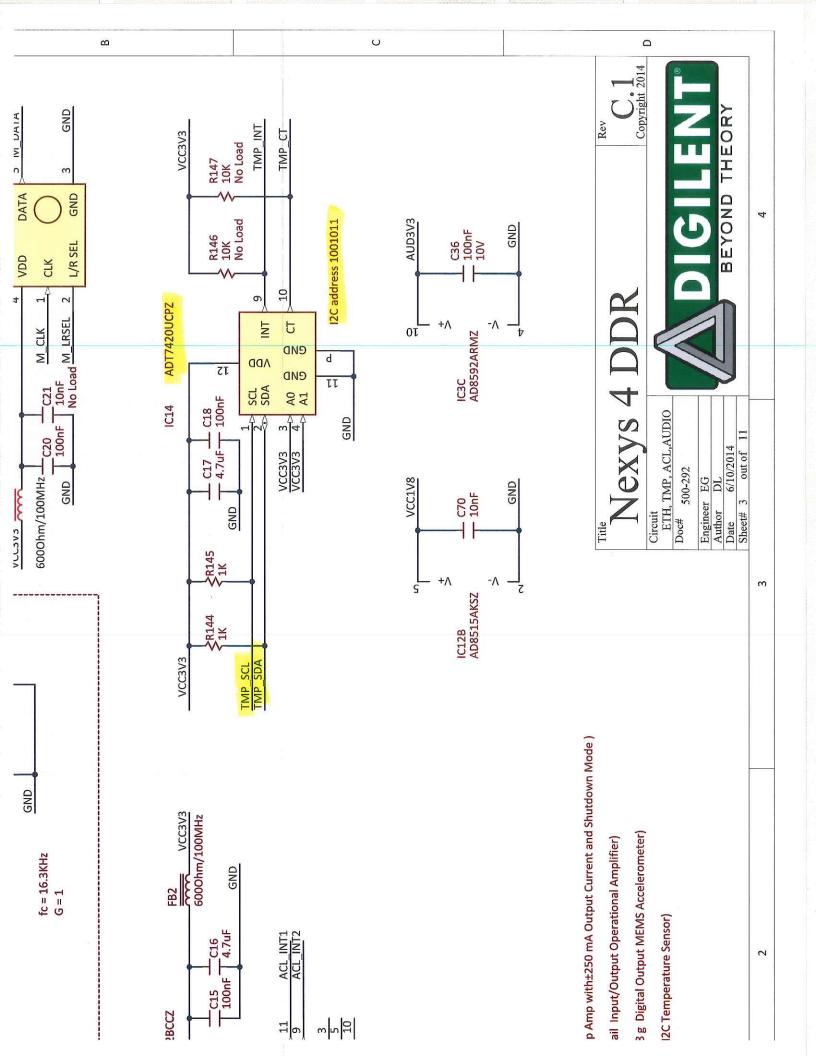

The Nexys4 DDR includes an Analog Device ADT7420 temperature sensor. The sensor provides up to 16-bit resolution with a typical accuracy better than 0.25 degrees Celsius. The interface between the temperature sensor and FPGA is shown in Figure 22.

Figure 22. Temperature sensor interface.

## 13.1 I2C Interface

The ADT7420 chip acts as a slave device using the industry standard I2C communication scheme. To communicate with ADT7420 chip, the I2C master must specify a slave address (0x4B) and a flag indicating whether the

communication is a read (1) or a write (0). Once specifications are made for communication, a data transfer takes place. For ADT7420, the data transfer should consist of the address of the desired device register followed by the data to be written to the specified register. To read from a register, the master must write the desired register address to the ADT7420, then send an I2C restart condition, and send a new read request to the ADT7420. If the master does not generate a restart condition prior to attempting the read, the value written to the address register will be reset to 0x00.

As some registers store 16-bit values as 8-bit register pairs, the ADT7420 will automatically increment the address register of the device when accessing certain registers, such as the temperature registers and the threshold registers. This allows for the master to use a single read or write request to access both the low and high bytes of these registers. A complete listing of registers and their behavior can be found in the ADT7420 datasheet available on the Analog Devices website.

# 13.2 Open Drain Outputs

The ADT7420 provides two open drain output signals to indicate when pre-set temperature thresholds are reached. If the temperature leaves a range defined by registers TLOW (0x06:0x07) and THIGH (0x04:0x05), the INT pin can be driven low or high based upon the configuration of the device. Similarly, the CT pin can be driven low or high if the temperature exceeds a critical threshold defined in TCRIT (0x08:0x09). Both of these pins need internal FPGA pull-ups when used.

For details on the electrical specifications and configuration of the INT and CT pins, refer to the ADT7420 datasheet.

# 13.3 Quick Start Operation

When the ADT7420 is powered up, it is in a mode that can be used as a simple temperature sensor without any initial configuration. By default, the device address register points to the temperature MSB register, so a two byte read without specifying a register will read the value of the temperature register from the device. The first byte read back will be the most significant byte (MSB) of the temperature data, and the second will be the least significant byte (LSB) of the data. These two bytes form a two's complement 16-bit integer. If the result is shifted to the right three bits and multiplied by 0.0625, the resulting signed floating point value will be a temperature reading in degrees Celsius.

For information on reading and writing to the other registers of the device, as well as notes on the accuracy of the temperature measurements, refer to the ADT7420 datasheet.

# 14 Accelerometer

The Nexys4 DDR includes an Analog Device ADXL362 accelerometer. The ADXL362 is a 3-axis MEMS accelerometer that consumes less than  $2\mu A$  at a 100Hz output data rate and 270nA when in motion triggered wake-up mode. Unlike accelerometers that use power duty cycling to achieve low power consumption, the ADXL362 does not alias input signals by under-sampling; it samples the full bandwidth of the sensor at all data rates. The ADXL362 always provides 12-bit output resolution; 8-bit formatted data is also provided for more efficient single-byte transfers when a lower resolution is sufficient. Measurement ranges of  $\pm 2$  g,  $\pm 4$  g, and  $\pm 8$  g are available with a resolution of 1 mg/LSB on the  $\pm 2$  g range. The FPGA can talk with the ADXL362 via SPI interface. While the ADXL362 is in Measurement Mode, it continuously measures and stores acceleration data in the X-data, Y-data, and Z-data registers. The interface between the FPGA and accelerometer can be seen in Figure 23.

# ±0.25°C Accurate, 16-Bit Digital I<sup>2</sup>C Temperature Sensor

**Data Sheet**

**ADT7420**

#### **FEATURES**

**High performance**

**Temperature accuracy**

±0.20°C from -10°C to +85°C at 3.0 V

±0.25°C from -20°C to +105°C from 2.7 V to 3.3 V

16-bit resolution: 0.0078°C

Ultralow temperature drift: 0.0073°C

NIST traceable or equivalent

Fast first temperature conversion on power-up of 6 ms

**Easy implementation**

No temperature calibration/correction required by user

No linearity correction required

Low power

Power-saving 1 sample per second (SPS) mode

700 µW typical at 3.3 V in normal mode

7 μW typical at 3.3 V in shutdown mode

Wide operating ranges

Temperature range: -40°C to +150°C

Voltage range: 2.7 V to 5.5 V

**Programmable interrupts**

Critical overtemperature interrupt

Overtemperature/undertemperature interrupt

I<sup>2</sup>C-compatible interface

16-lead, 4 mm × 4 mm LFCSP RoHS-compliant package

#### **APPLICATIONS**

RTD and thermistor replacement

Thermocouple cold junction compensation

**Medical equipment**

**Industrial control and test**

Food transportation and storage

**Environmental monitoring and HVAC**

Laser diode temperature control

#### **GENERAL DESCRIPTION**

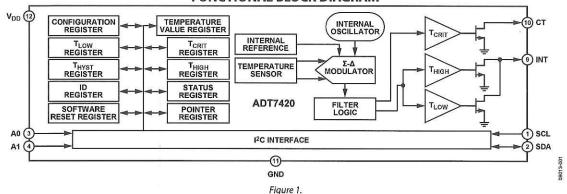

The ADT7420 is a high accuracy digital temperature sensor offering breakthrough performance over a wide industrial range, housed in a 4 mm  $\times$  4 mm LFCSP package. It contains an internal band gap reference, a temperature sensor, and a 16-bit ADC to monitor and digitize the temperature to 0.0078°C resolution. The ADC resolution, by default, is set to 13 bits (0.0625°C). The ADC resolution is a user programmable mode that can be changed through the serial interface.

The ADT7420 is guaranteed to operate over supply voltages from 2.7 V to 5.5 V. Operating at 3.3 V, the average supply current is typically 210  $\mu A$ . The ADT7420 has a shutdown mode that powers down the device and offers a shutdown current of typically 2.0  $\mu A$  at 3.3 V. The ADT7420 is rated for operation over the  $-40^{\circ}C$  to  $+150^{\circ}C$  temperature range.

Pin A0 and Pin A1 are available for address selection, giving the ADT7420 four possible I²C addresses. The CT pin is an opendrain output that becomes active when the temperature exceeds a programmable critical temperature limit. The INT pin is also an open-drain output that becomes active when the temperature exceeds a programmable limit. The INT pin and CT pin can operate in comparator and interrupt event modes.

#### **PRODUCT HIGHLIGHTS**

- 1. Ease of use, no calibration or correction required by the user.

- 2. Low power consumption.

- 3. Excellent long-term stability and reliability.

- 4. High accuracy for industrial, instrumentation, and medical applications.

- Packaged in a 16-lead, 4 mm × 4 mm LFCSP RoHScompliant package.

#### **FUNCTIONAL BLOCK DIAGRAM**

Rev. 0

| Document Feedback | Information furnished by Analog Devices is believed to be accurate and reliable to responsibility is assumed by Analog Devices for its use, nor for any infringements of nateurs or other than the property of t

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Spedifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2012 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

Data Sheet ADT7420

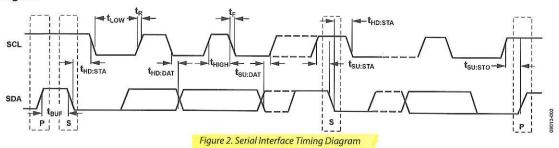

## I<sup>2</sup>C TIMING SPECIFICATIONS

$T_A = -40$ °C to +150°C,  $V_{DD} = 2.7$  V to 5.5 V, unless otherwise noted. All input signals are specified with rise time ( $t_R$ ) = fall time ( $t_F$ ) = 5 ns (10% to 90% of  $V_{DD}$ ) and timed from a voltage level of 1.6 V.

Table 2.

| Parameter                                                          | Min  | Тур | Max | Unit | Test Conditions/Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|--------------------------------------------------------------------|------|-----|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SERIAL INTERFACE <sup>1</sup>                                      |      |     |     |      | See Figure 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| SCL Frequency                                                      | 0    |     | 400 | kHz  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| SCL High Pulse Width, t <sub>HIGH</sub>                            | 0.6  |     |     | μs   | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| SCL Low Pulse Width, t <sub>LOW</sub>                              | 1.3  | (8) |     | μs   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| SCL, SDA Rise Time, t <sub>R</sub>                                 |      |     | 0.3 | μs   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| SCL, SDA Fall Time, t <sub>F</sub>                                 |      |     | 0.3 | μs   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Hold Time (Start Condition), thoista                               |      |     |     | μs   | After this period, the first clock is generated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Setup Time (Start Condition), tsu:sta                              |      |     |     | μs   | Relevant for repeated start condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| Data Setup Time, t <sub>SU:DAT</sub>                               | 0.02 |     |     | μs   | S CONTRACTOR COMMUNICATION CONTRACTOR CONTRA |  |

| Setup Time (Stop Condition), tsussto                               |      |     |     | μs   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Data Hold Time, t <sub>HD:DAT</sub> (Master)                       |      |     |     | μs   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Bus-Free Time (Between Stop and Start Condition), t <sub>BUF</sub> | 1.3  |     |     | μs   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Capacitive Load for Each Bus Line, CB                              |      |     | 400 | pF   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

<sup>&</sup>lt;sup>1</sup> Sample tested during initial release to ensure compliance.

#### **Timing Diagram**

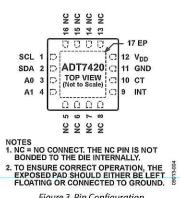

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 3. Pin Configuration

**Table 4. Pin Function Descriptions**

| Pin No. | Mnemonic        | Description                                                                                                                                                                                                               |

|---------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | SCL             | I <sup>2</sup> C Serial Clock Input. The serial clock is used to clock in and clock out data to and from any register of the ADT7420. Open-drain configuration. A pull-up resistor is required, typically 10 k $\Omega$ . |

| 2       | SDA             | I <sup>2</sup> C Serial Data Input/Output. Serial data to and from the part is provided on this pin. Open-drain configuration. A pull-up resistor is required, typically 10 k $\Omega$ .                                  |

| 3       | A0              | I <sup>2</sup> C Serial Bus Address Selection Pin. Logic input. Connect to GND or V <sub>DD</sub> to set an I <sup>2</sup> C address.                                                                                     |

| 4       | A1              | I <sup>2</sup> C Serial Bus Address Selection Pin. Logic input. Connect to GND or V <sub>DD</sub> to set an I <sup>2</sup> C address.                                                                                     |

| 5       | NC              | No Connect. The NC pin is not bonded to the die internally.                                                                                                                                                               |

| 6       | NC              | No Connect. The NC pin is not bonded to the die internally.                                                                                                                                                               |

| 7       | NC              | No Connect. The NC pin is not bonded to the die internally.                                                                                                                                                               |

| 8       | NC              | No Connect. The NC pin is not bonded to the die internally.                                                                                                                                                               |

| 9       | INT             | Overtemperature and Undertemperature Indicator. Logic output. Power-up default setting is as an active low comparator interrupt. Open-drain configuration. A pull-up resistor is required, typically 10 k $\Omega$ .      |

| 10      | СТ              | Critical Overtemperature Indicator. Logic output. Power-up default polarity is active low. Open-drain configuration. A pull-up resistor is required, typically 10 kΩ.                                                     |

| 11      | GND             | Analog and Digital Ground.                                                                                                                                                                                                |

| 12      | V <sub>DD</sub> | Positive Supply Voltage (2.7 V to 5.5 V). The supply should be decoupled with a 0.1 μF ceramic capacitor to ground.                                                                                                       |

| 13      | NC              | No Connect. The NC pin is not bonded to the die internally.                                                                                                                                                               |

| 14      | NC              | No Connect. The NC pin is not bonded to the die internally.                                                                                                                                                               |

| 15      | NC              | No Connect. The NC pin is not bonded to the die internally.                                                                                                                                                               |

| 16      | NC              | No Connect. The NC pin is not bonded to the die internally.                                                                                                                                                               |

| 17      | EP              | Exposed Pad. To ensure correct operation, the exposed pad should either be left floating or connected to ground.                                                                                                          |

ADT7420 Data Sheet

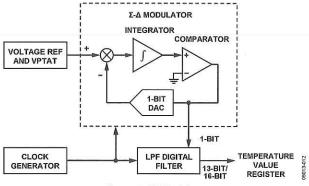

# THEORY OF OPERATION CIRCUIT INFORMATION

The ADT7420 is a high accuracy digital temperature sensor that uses a 16-bit ADC to monitor and digitize the temperature to 0.0078°C of resolution. The ADC resolution, by default, is set to 13 bits (0.0625°C). An internal temperature sensor generates a voltage proportional to absolute temperature, which is compared to an internal voltage reference and input into a precision digital modulator.

The internal temperature sensor has high accuracy and linearity over the entire rated temperature range without needing correction or calibration by the user.

The sensor output is digitized by a sigma-delta  $(\Sigma - \Delta)$  modulator, also known as the charge balance type analog-to-digital converter. This type of converter utilizes time-domain oversampling and a high accuracy comparator to deliver 16 bits of resolution in an extremely compact circuit.

#### **CONVERTER DETAILS**

The  $\Sigma$ - $\Delta$  modulator consists of an input sampler, a summing network, an integrator, a comparator, and a 1-bit DAC. This architecture creates a negative feedback loop and minimizes the integrator output by changing the duty cycle of the comparator output in response to input voltage changes. The comparator samples the output of the integrator at a much higher rate than the input sampling frequency. This oversampling spreads the quantization noise over a much wider band than that of the input signal, improving overall noise performance and increasing accuracy.

Figure 11. Σ-Δ Modulator

The ADT7420 can be configured to operate in any one of the following four operating modes: normal, one-shot, 1 SPS, and shutdown.

#### **NORMAL MODE**

In normal mode (default power-up mode) the ADT7420 runs an automatic conversion sequence. During this automatic conversion sequence, a conversion typically takes 240 ms to complete and the ADT7420 is continuously converting. This means that as soon as one temperature conversion is completed, another temperature conversion begins. Each temperature conversion result is stored in the temperature value registers and is available through the I<sup>2</sup>C interface. In continuous conversion mode, the read operation provides the most recent converted result.

On power-up, the first conversion is a fast conversion, taking typically 6 ms. If the temperature exceeds 147°C, the CT pin asserts low. If the temperature exceeds 64°C, the INT pin asserts low. Fast conversion temperature accuracy is typically within ±5°C.

The conversion clock for the part is generated internally. No external clock is required except when reading from and writing to the serial port.

The measured temperature value is compared with a critical temperature limit (stored in the 16-bit  $T_{\text{CRIT}}$  setpoint read/write register), a high temperature limit (stored in the 16-bit  $T_{\text{HIGH}}$  setpoint read/write register), and a low temperature limit (stored in the 16-bit  $T_{\text{LOW}}$  setpoint read/write register). If the measured value exceeds these limits, the INT pin is activated; and if it exceeds the  $T_{\text{CRIT}}$  limit, the CT pin is activated. The INT and CT pins are programmable for polarity via the configuration register, and the INT and CT pins are also programmable for interrupt mode via the configuration register.

#### **ONE-SHOT MODE**

Setting Bit 6 to 0 and Bit 5 to 1 of the configuration register (Register Address 0x03) enables the one-shot mode. When this mode is enabled, the ADT7420 immediately completes a conversion and then goes into shutdown mode.

Wait for a minimum of 240 ms after writing to the operation mode bits before reading back the temperature from the temperature value register. This time ensures that the ADT7420 has time to power up and complete a conversion.

To obtain an updated temperature conversion, reset Bit 6 to 0 and Bit 5 to 1 in the configuration register (0x03).

The one-shot mode is useful when one of the circuit design priorities is to reduce power consumption.

#### **TEMPERATURE DATA FORMAT**

One LSB of the ADC corresponds to 0.0625°C in 13-bit mode or 0.0078°C in 16-bit mode. The ADC can theoretically measure a temperature range of 255°C, but the ADT7420 is guaranteed to measure a low value temperature limit of  $-40^{\circ}$ C to a high value temperature limit of  $+150^{\circ}$ C. The temperature measurement result is stored in the 16-bit temperature value register and is compared with the high temperature limits stored in the  $T_{\text{CRIT}}$  setpoint register and the  $T_{\text{HIGH}}$  setpoint register. It is also compared with the low temperature limit stored in the  $T_{\text{LOW}}$  setpoint register.

Temperature data in the temperature value register, the  $T_{\text{CRIT}}$  setpoint register, the  $T_{\text{HIGH}}$  setpoint register, and the  $T_{\text{LOW}}$  setpoint register are represented by a 13-bit twos complement word. The MSB is the temperature sign bit. The three LSBs, Bit 0 to Bit 2, on power-up, are not part of the temperature conversion result and are flag bits for  $T_{\text{CRIT}}$ ,  $T_{\text{HIGH}}$ , and  $T_{\text{LOW}}$ . Table 5 shows the 13-bit temperature data format without Bit 0 to Bit 2.

The number of bits in the temperature data-word can be extended to 16 bits, twos complement, by setting Bit 7 to 1 in the configuration register (Register Address 0x03). When using a 16-bit temperature data value, Bit 0 to Bit 2 are not used as flag bits and are, instead, the LSB bits of the temperature value. The power-on default setting has a 13-bit temperature data value.

Reading back the temperature from the temperature value register requires a 2-byte read. Designers that use a 9-bit temperature data format can still use the ADT7420 by ignoring the last four LSBs of the 13-bit temperature value. These four LSBs are Bit 6 to Bit 3 in Table 5.

Table 5. 13-Bit Temperature Data Format

| Temperature | Digital Output<br>(Binary) Bits[15:3] | Digital Output (Hex) |

|-------------|---------------------------------------|----------------------|

| −40°C       | 1 1101 1000 0000                      | 0x1D80               |

| −25°C       | 1 1110 0111 0000                      | 0x1E70               |

| −0.0625°C   | 1 1111 1111 1111                      | 0x1FFF               |

| 0°C         | 0 0000 0000 0000                      | 0x000                |

| +0.0625°C   | 0 0000 0000 0001                      | 0x001                |

| +25°C       | 0 0001 1001 0000                      | 0x190                |

| +105°C      | 0 0110 1001 0000                      | 0x690                |

| +125°C      | 0 0111 1101 0000                      | 0x7D0                |

| +150°C      | 0 1001 0110 0000                      | 0x960                |

#### **TEMPERATURE CONVERSION FORMULAS**

#### 16-Bit Temperature Data Format

Positive Temperature = ADC Code (dec)/128

Negative Temperature =  $(ADC\ Code\ (dec) - 65,536)/128$  where  $ADC\ Code$  uses all 16 bits of the data byte, including the sign bit.

Negative Temperature =  $(ADC\ Code\ (dec) - 32,768)/128$  where Bit 15 (sign bit) is removed from the ADC code.

#### 13-Bit Temperature Data Format

Positive Temperature = ADC Code (dec)/16

Negative Temperature =  $(ADC\ Code\ (dec) - 8192)/16$

where *ADC Code* uses the first 13 MSBs of the data byte, including the sign bit.

Negative Temperature =  $(ADC\ Code\ (dec) - 4096)/16$  where Bit 15 (sign bit) is removed from the ADC code.

#### 10-Bit Temperature Data Format

Positive Temperature = ADC Code (dec)/2

Negative Temperature =  $(ADC\ Code\ (dec)-1024)/2$  where  $ADC\ Code$  uses all 10 bits of the data byte, including the sign bit.

Negative Temperature =  $(ADC\ Code\ (dec) - 512)/2$  where Bit 9 (sign bit) is removed from the ADC code.

#### 9-Bit Temperature Data Format

Positive Temperature = ADC Code (dec)

Negative Temperature = ADC Code (dec) -512 where ADC Code uses all nine bits of the data byte, including the sign bit.

Negative Temperature = ADC Code (dec) - 256 where Bit 8 (sign bit) is removed from the ADC code.

Data Sheet ADT7420

# REGISTERS

The ADT7420 contains 14 registers:

- Nine temperature registers

- A status register

- An ID register

- A configuration register

- An address pointer register

- A software reset

All registers are eight bits wide. The temperature value registers, the status register, and the ID register are read-only. The software reset is a write-only register. On power-up, the address pointer register is loaded with 0x00 and points to the temperature value most significant byte register (Register Address 0x00).

Table 6. ADT7420 Registers

| Register<br>Address | Description                                       | Power-On<br>Default |  |

|---------------------|---------------------------------------------------|---------------------|--|

| 0x00                | Temperature value most significant byte           | 0x00                |  |

| 0x01                | Temperature value least significant byte          | 0x00                |  |

| 0x02                | Status                                            | 0x00                |  |

| 0x03                | Configuration                                     | 0x00                |  |

| 0x04                | T <sub>HIGH</sub> setpoint most significant byte  | 0x20 (64°C)         |  |

| 0x05                | T <sub>HIGH</sub> setpoint least significant byte | 0x00 (64°C)         |  |

| 0x06                | T <sub>LOW</sub> setpoint most significant byte   | 0x05 (10°C)         |  |

| 0x07                | T <sub>LOW</sub> setpoint least significant byte  | 0x00 (10°C)         |  |

| 80x0                | T <sub>CRIT</sub> setpoint most significant byte  | 0x49 (147°C)        |  |

| 0x09                | T <sub>CRIT</sub> setpoint least significant byte | 0x80 (147°C)        |  |

| 0x0A                | T <sub>HYST</sub> setpoint                        | 0x05 (5°C)          |  |

| 0x0B                | ID                                                | 0xCB                |  |

| 0x2F                | Software reset                                    | 0xXX                |  |

#### **ADDRESS POINTER REGISTER**

This register is always the first register written to during a write to the ADT7420. It should be set to the address of the register to which the write or read transaction is intended. Table 7 shows the register address of each register on the ADT7420. The default value of the address pointer register is 0x00.

Table 7. Address Pointer Register

| P7   | P6   | P5   | P4   | Р3   | P2   | P1   | PO   |

|------|------|------|------|------|------|------|------|

| ADD7 | ADD6 | ADD5 | ADD4 | ADD3 | ADD2 | ADD1 | ADD0 |

#### **TEMPERATURE VALUE REGISTERS**

The temperature value consists of two bytes, one most significant byte and one least significant byte. These values can be read in two separate 1-byte reads or in a single 2-byte read. For a 2-byte read, only the address of the most significant byte must be loaded into the address pointer register. After the most significant byte is read, the address pointer is auto-incremented so that the least significant byte can read within the same transaction.

Bit 0 to Bit 2 are event alarm flags for  $T_{\text{LOW}}$ ,  $T_{\text{HIGH}}$ , and  $T_{\text{CRIT}}$ . When the ADC is configured to convert the temperature to a 16-bit digital value, then Bit 0 to Bit 2 are no longer used as flag bits and are instead used as the LSBs for the extended digital value.

Table 8. Temperature Value MSB Register (Register Address 0x00)

| Bit    | Bit         Default Value         Type         Name           [14:8]         0000000         R         Temp |   | Name | Description                                                          |  |  |  |

|--------|-------------------------------------------------------------------------------------------------------------|---|------|----------------------------------------------------------------------|--|--|--|

| [14:8] |                                                                                                             |   | Temp | Temperature value in twos complement format                          |  |  |  |

| 15     | 0                                                                                                           | R | Sign | Sign bit, indicates if the temperature value is negative or positive |  |  |  |

Table 9. Temperature Value LSB Register (Register Address 0x01)

| Bit   | Default<br>Value | Туре | Name                        | Description                                                                                                                                                                        |

|-------|------------------|------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | 0                | R    | T <sub>LOW</sub> flag/LSB0  | Flags a $T_{LOW}$ event if the configuration register, Register Address $0x03[7] = 0$ (13-bit resolution). When the temperature value is below $T_{LOW}$ , this bit it set to 1.   |

|       |                  |      |                             | Contains the Least Significant Bit 0 of the 15-bit temperature value if the configuration register, Register Address 0x03[7] = 1 (16-bit resolution).                              |

| 1     | 0                | R    | T <sub>HIGH</sub> flag/LSB1 | Flags a $T_{HIGH}$ event if the configuration register, Register Address $0x03[7] = 0$ (13-bit resolution). When the temperature value is above $T_{HIGH}$ , this bit it set to 1. |

|       |                  |      | 101<br>E3                   | Contains the Least Significant Bit 1 of the 15-bit temperature value if the configuration register, Register Address 0x03[7] = 1 (16-bit resolution).                              |

| 2     | 0                | R    | T <sub>CRIT</sub> flag/LSB2 | Flags a $T_{CRIT}$ event if the configuration register, Register Address 0x03[7] = 0 (13-bit resolution). When the temperature value exceeds $T_{CRIT}$ , this bit it set to 1.    |

|       |                  |      |                             | Contains the Least Significant Bit 2 of the 15-bit temperature value if the configuration register, Register Address 0x03[7] = 1 (16-bit resolution).                              |

| [7:3] | 00000            | R    | Temp                        | Temperature value in twos complement format.                                                                                                                                       |

Data Sheet ADT7420

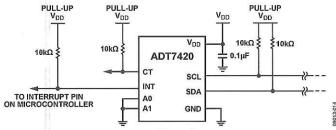

# **SERIAL INTERFACE**

Figure 13. Typical I<sup>2</sup>C Interface Connection

Control of the ADT7420 is carried out via the I<sup>2</sup>C-compatible serial interface. The ADT7420 is connected to this bus as a slave and is under the control of a master device.

Figure 13 shows a typical I2C interface connection.

#### **SERIAL BUS ADDRESS**

Like most I²C-compatible devices, the ADT7420 has a 7-bit serial address. The five MSBs of this address for the ADT7420 are hardwired internally to 10010. Pin A1 and Pin A0 set the two LSBs. These pins can be configured two ways, low and high, to give four different address options. Table 20 shows the different bus address options available. The recommended pull-up resistor value on the SDA and SCL lines is  $10\ k\Omega$ .

Table 20. I2C Bus Address Options

| Binary |    |    |    |    |    |    |      |

|--------|----|----|----|----|----|----|------|

| A6     | A5 | A4 | Аз | A2 | A1 | AO | Hex  |

| 1      | 0  | 0  | 1  | 0  | 0  | 0  | 0x48 |

| 1      | 0  | 0  | 1  | 0  | 0  | 1  | 0x49 |

| 1      | 0  | 0  | 1  | 0  | 1  | 0  | 0x4A |

| 1      | 0  | 0  | 1  | 0  | 1  | 1  | 0x4B |

The serial bus protocol operates as follows:

1. The master initiates data transfer by establishing a start condition, defined as a high-to-low transition on the serial data line, SDA, while the serial clock line, SCL, remains high. This indicates that an address/data stream is going to follow. All slave peripherals connected to the serial bus respond to the start condition and shift in the next eight bits, consisting of a 7-bit address (MSB first) plus a read/write (R/W) bit. The R/W bit determines whether data is written to, or read from, the slave device.

- 2. The peripheral with the address corresponding to the transmitted address responds by pulling the data line low during the low period before the ninth clock pulse, known as the acknowledge bit. All other devices on the bus then remain idle while the selected device waits for data to be read from or written to it. If the R/W bit is a 0, the master writes to the slave device. If the R/W bit is a 1, the master reads from the slave device.

- 3. Data is sent over the serial bus in sequences of nine clock pulses, eight bits of data followed by an acknowledge bit from the receiver of data. Transitions on the data line must occur during the low period of the clock signal and remain stable during the high period as a low-to-high transition when the clock is high, which can be interpreted as a stop signal.

- 4. When all data bytes have been read or written, stop conditions are established. In write mode, the master pulls the data line high during the 10<sup>th</sup> clock pulse to assert a stop condition. In read mode, the master device pulls the data line high during the low period before the ninth clock pulse. This is known as a no acknowledge. The master takes the data line low during the low period before the 10<sup>th</sup> clock pulse, then high during the 10<sup>th</sup> clock pulse to assert a stop condition.

It is not possible to mix read and write in one operation because the type of operation is determined at the beginning and cannot subsequently be changed without starting a new operation. ADT7420

**Data Sheet**

#### **WRITING DATA**

It is possible to write either a single byte of data or two bytes to the ADT7420, depending on which registers are to be written.

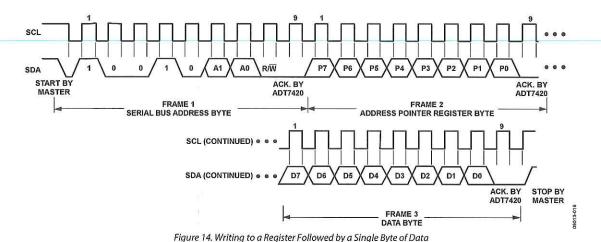

Writing a single byte of data requires the serial bus address, the data register address written to the address pointer register, followed by the data byte written to the selected data register. This is shown in Figure 14.

For the  $T_{\rm HIGH}$  setpoint,  $T_{\rm LOW}$  setpoint, and  $T_{\rm CRIT}$  setpoint registers, it is possible to write to both the MSB and the LSB registers in the same write transaction. Writing two bytes of data to these registers requires the serial bus address, the data register address of the MSB register written to the address pointer register, followed by the two data bytes written to the selected data register. This is shown in Figure 15.

If more than the required number of data bytes is written to a register, the register ignores these extra data bytes. To write to a different register, a start or repeated start is required.

SCL A1 A0 R/W P7 P6 P5 P3 P2 SDA START BY ACK. BY ADT7420 ACK. BY ADT7420 MASTER FRAME 1 FRAME 2 SERIAL BUS ADDRESS BYTE ADDRESS POINTER REGISTER BYTE SCL (CONTINUED) SDA (CONTINUED) e e D15 D14 D13 D11 D10 D9 D8 D7 D2 D12 D6 D5 D4 D3 D1 DO ACK. BY STOP BY ADT7420 ADT7420 MASTER FRAME 3 FRAME 4

Figure 15. Writing to a Register Followed by Two Bytes of Data

Data Sheet ADT7420

#### **READING DATA**

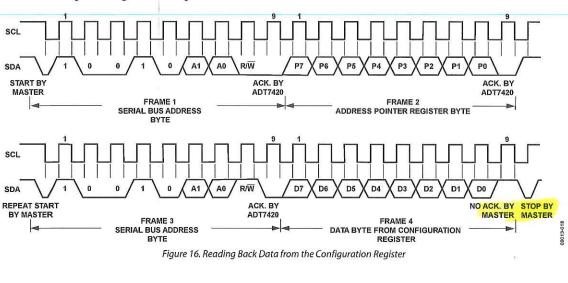

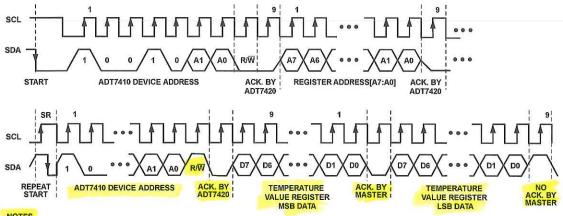

Reading data from the ADT7420 is done in a single data byte operation for the configuration register, the status register, the THYST setpoint register, and the ID register. A two data byte read operation is needed for the temperature value register, THIGH setpoint register, TLOW setpoint register, and the TCRIT setpoint register. Reading back the contents of an 8-bit register similar to the configuration register is shown in Figure 16. Reading back the contents of the temperature value register is shown in Figure 17.

Reading back from any register first requires a single-byte write operation to the address pointer register to set up the address of the register that is going to be read from. In the case of reading back from the 2-byte registers, the address pointer automatically increments from the MSB register address to the LSB register address.

To read from another register, execute another write to the address pointer register to set up the relevant register address. Thus, block reads are not possible, that is, there is no I2C address pointer auto-increment except when reading back from a 16-bit register. If the address pointer register has previously been set up with the address of the register that is going to receive a read command, there is no need to repeat a write operation to set up the register address again.

1. A START CONDITION AT THE BEGINNING IS DEFINED AS A HIGH-TO-LOW TRANSITION ON SDA WHILE SCL REMAINS HIGH.

- 2. A STOP CONDITION AT THE END IS DEFINED AS A LOW-TO-HIGH TRANSITION ON SDA WHILE SCL. REMAINS HIGH. 3. THE MASTER GENERATES THE NO ACKNOWLEDGE AT THE END OF THE READBACK TO SIGNAL THAT IT DOES NOT WANT ADDITIONAL DATA.

- 4. TEMPERATURE VALUE REGISTER MSB DATA AND TEMPERATURE VALUE REGISTER LSB DATA ARE ALWAYS SEPARATED BY A LOW ACK BIT. 5. THE RW BIT IS SET TO A1 TO INDICATE A READBACK OPERATION.

Figure 17. Reading Back Data from the Temperature Value Register