This tutorial shows how to create a simple project using a DCM (Digital Clock Manager).

(Jim Duckworth/Myo Thaw – August 2012)

The DCM generates 50MHz and 25MHz signals from the 50MHz xtal clock connected to the FPGA.

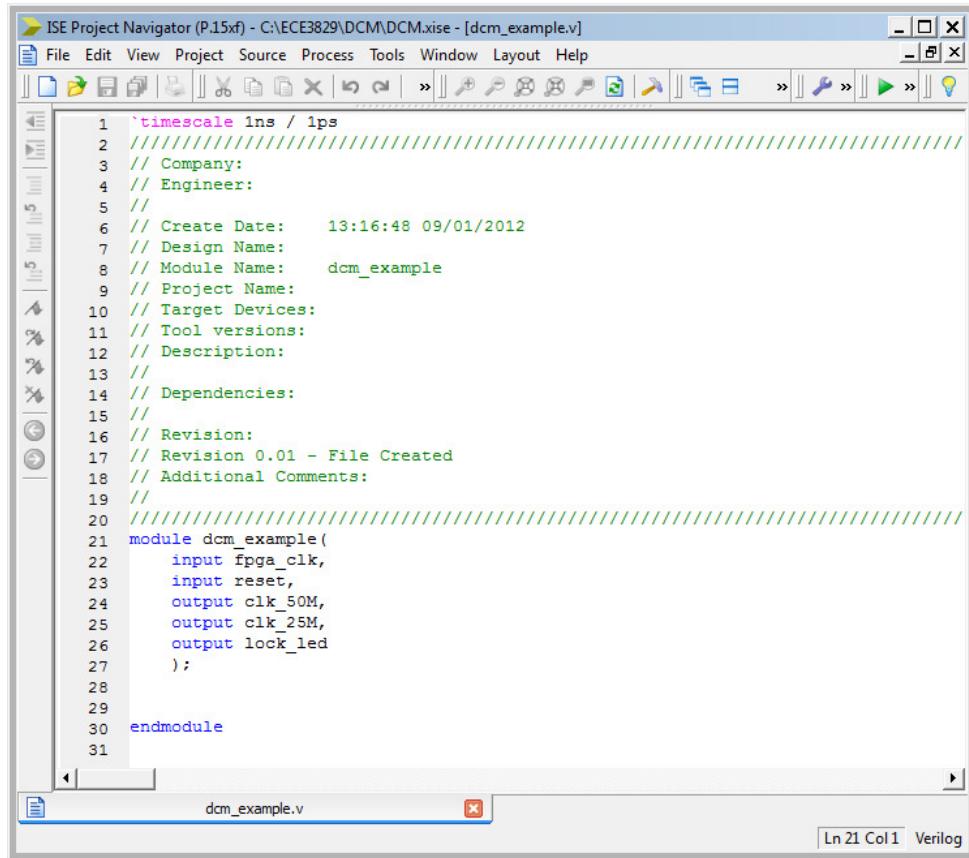

Create a simple module with the following ports:

```

1 `timescale 1ns / 1ps

2 //////////////////////////////////////////////////////////////////

3 // Company:

4 // Engineer:

5 //

6 // Create Date: 13:16:48 09/01/2012

7 // Design Name:

8 // Module Name: dcm_example

9 // Project Name:

10 // Target Devices:

11 // Tool versions:

12 // Description:

13 //

14 // Dependencies:

15 //

16 // Revision:

17 // Revision 0.01 - File Created

18 // Additional Comments:

19 //

20 //////////////////////////////////////////////////////////////////

21 module dcm_example(

22     input fpga_clk,

23     input reset,

24     output clk_50M,

25     output clk_25M,

26     output lock_led

27 );

28

29

30 endmodule

31

```

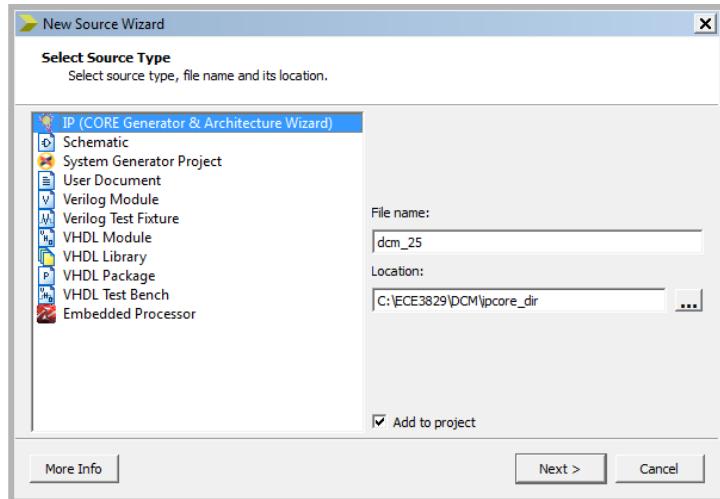

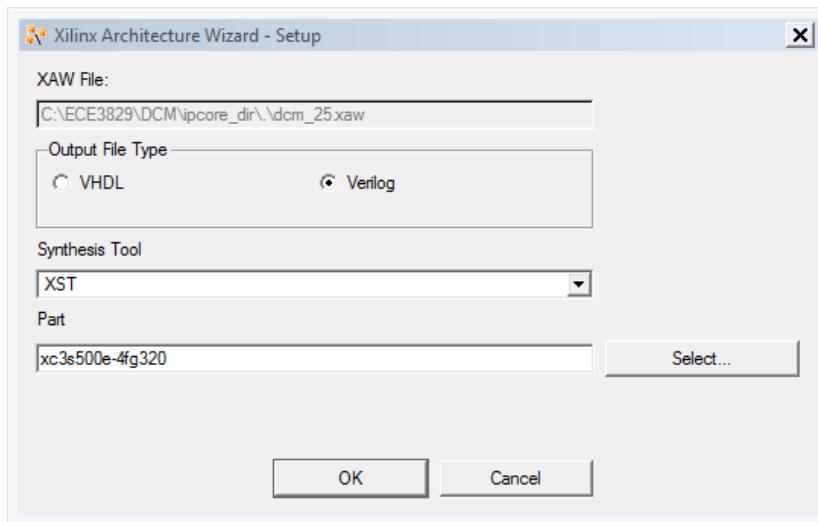

Add a new IP source: Call it dcm\_25 (for 25MHz DCM)

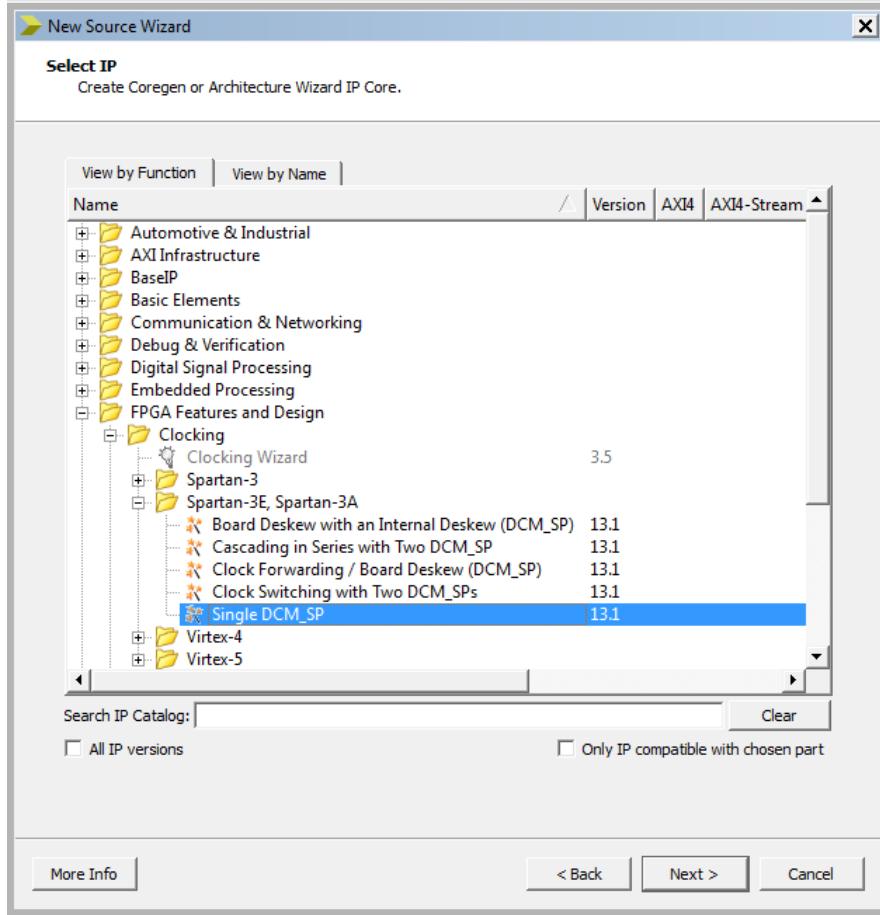

Select the Single DCM\_SP core:

Click Next and then Finish.

Click OK

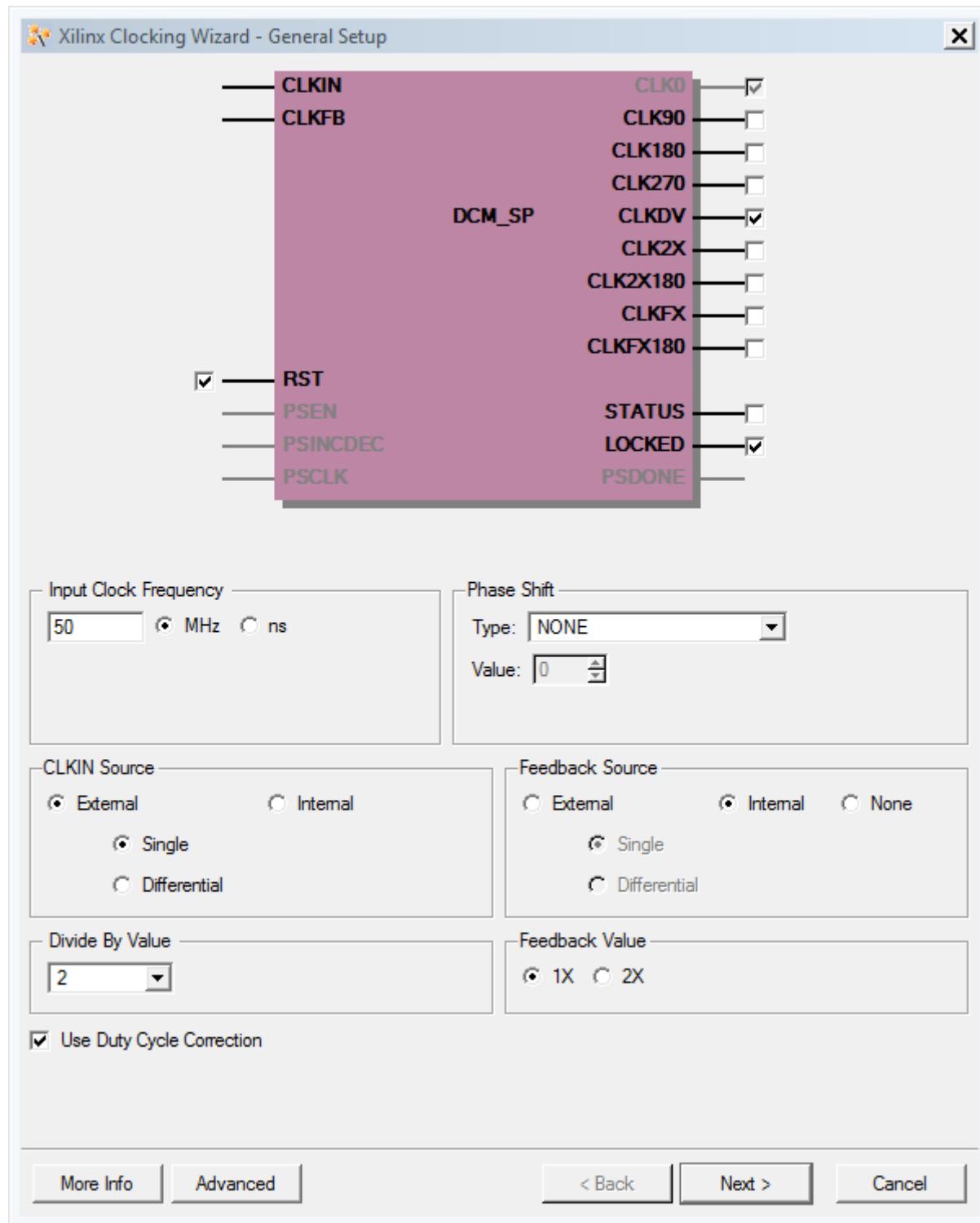

Click the LOCKED, and CLKDV pin options and enter 50 for the Input Frequency and Select 2 for the Divide by Value

Click Next, Next, and Finish

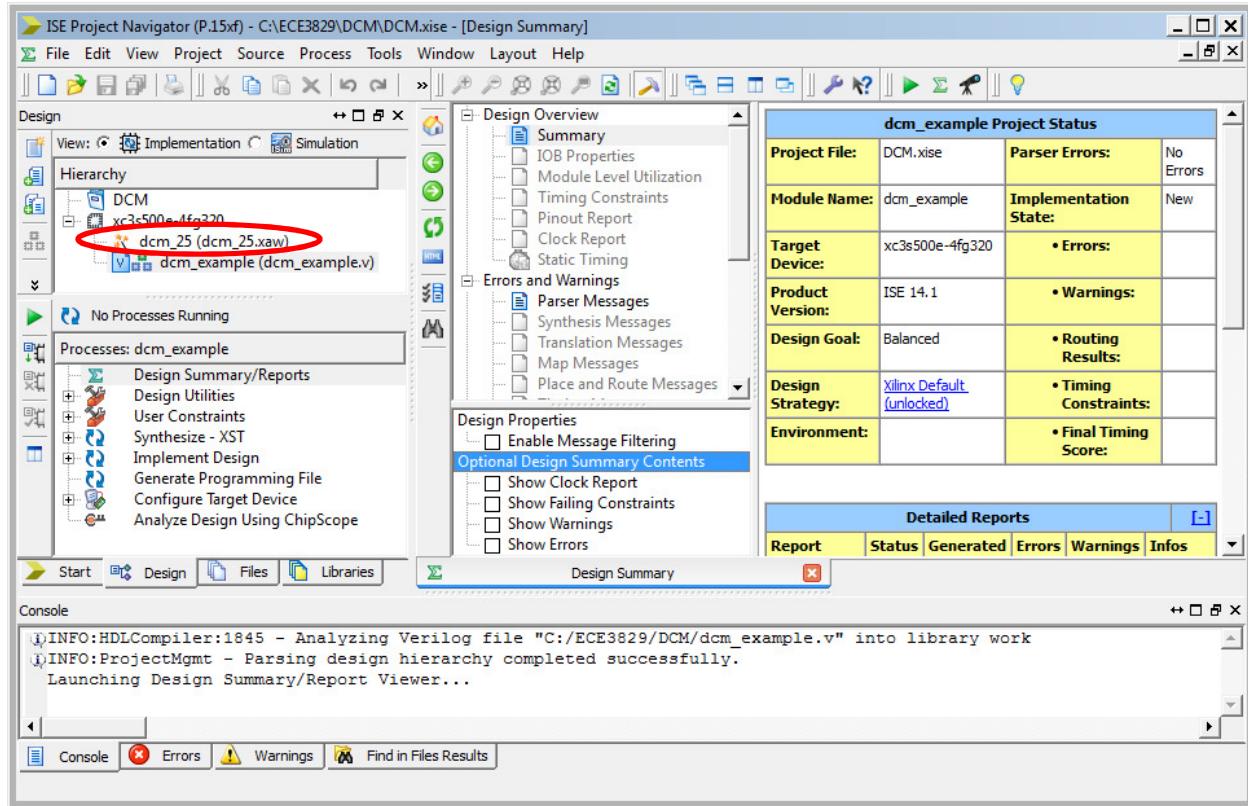

You can now see the dcm\_25 in the Design pane,

Select it and you will see some options in the Processes pane.

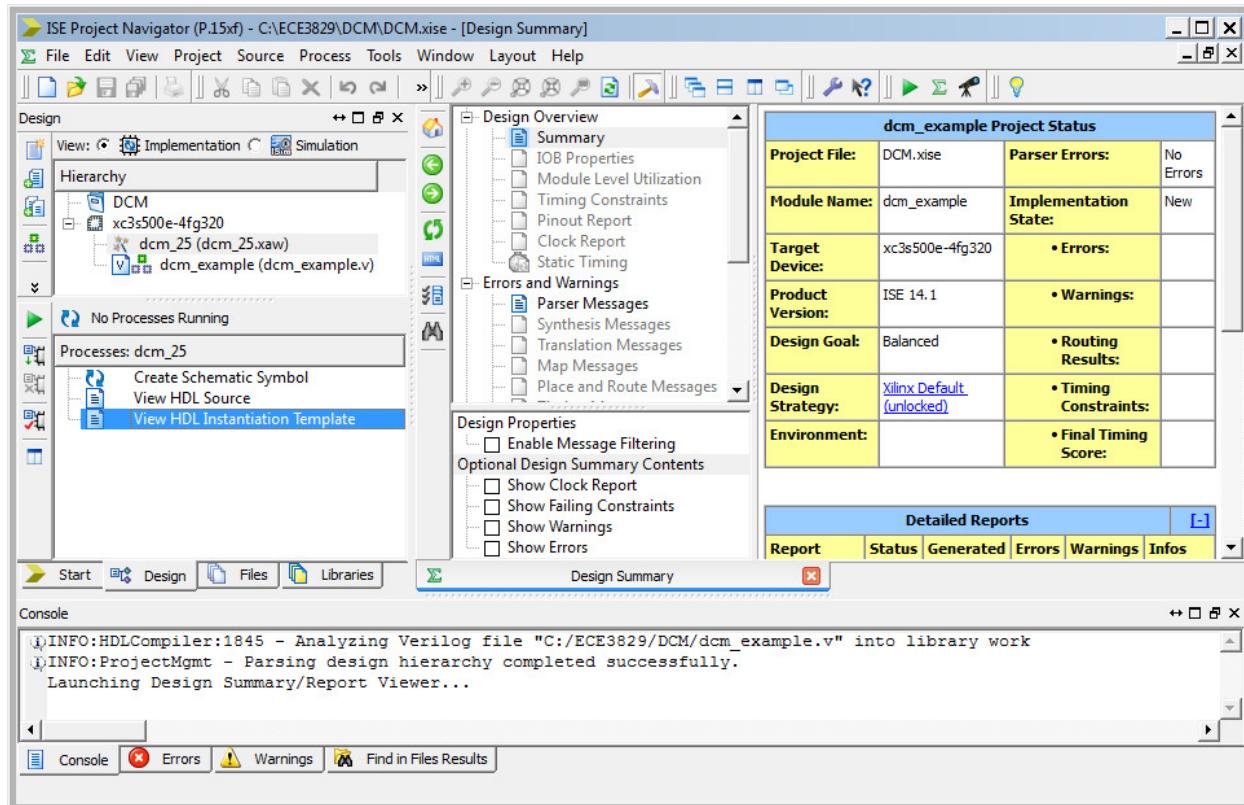

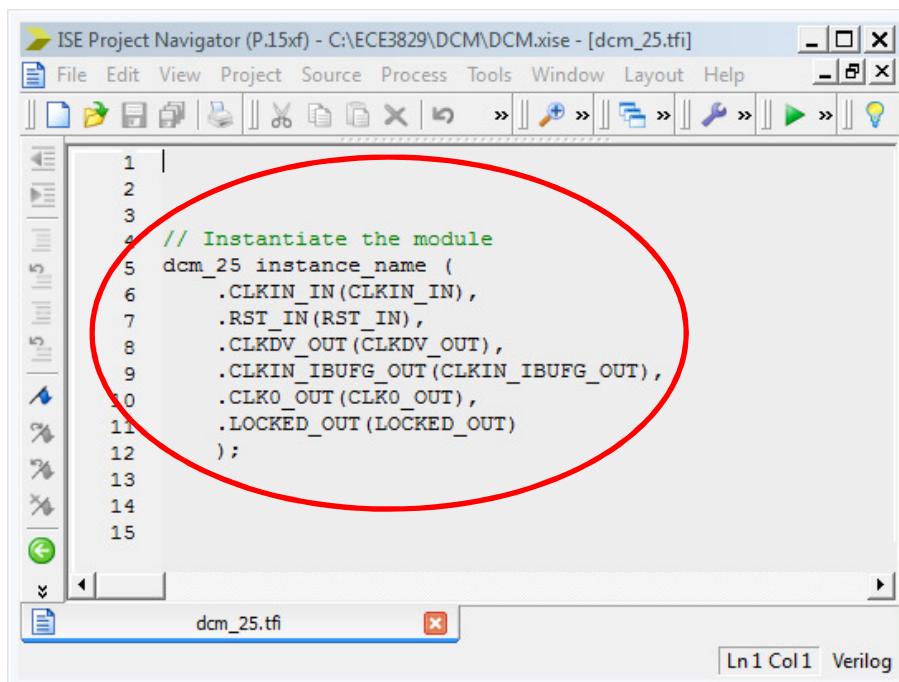

Select the View HDL Instantiation Template

Double –click the *View HDL Instantiation Template* process:

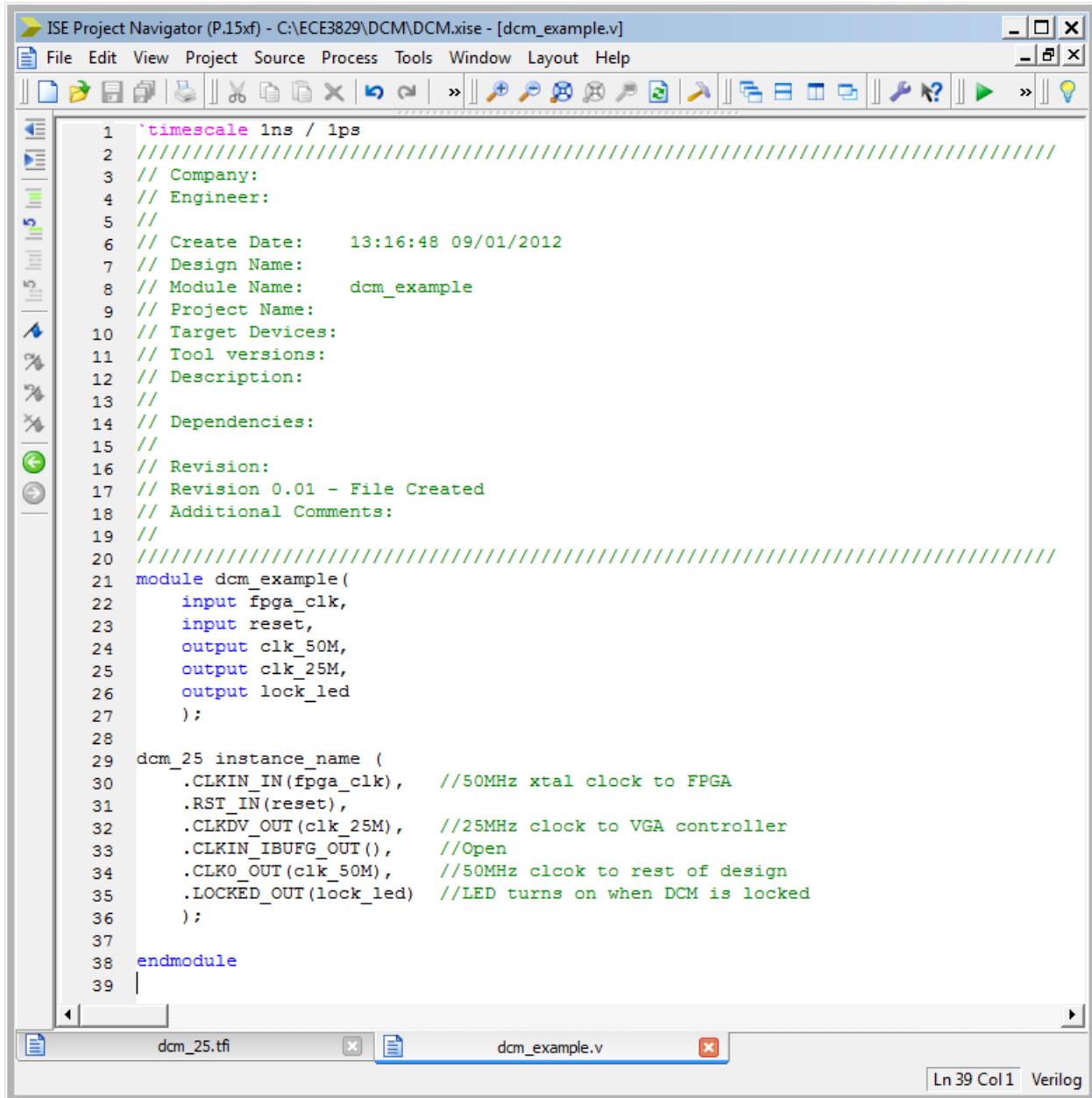

Copy and Paste the DCM instantiation templates to your original Verilog:

The screenshot shows the ISE Project Navigator interface with a Verilog file 'dcm\_example.v' open. The code in the editor is as follows:

```

1 `timescale 1ns / 1ps

2 // Company:

3 // Engineer:

4 //

5 // Create Date: 13:16:48 09/01/2012

6 // Design Name:

7 // Module Name: dcm_example

8 // Project Name:

9 // Target Devices:

10 // Tool versions:

11 // Description:

12 //

13 //

14 // Dependencies:

15 //

16 // Revision:

17 // Revision 0.01 - File Created

18 // Additional Comments:

19 //

20 ///////////////////////////////////////////////////

21 module dcm_example(

22     input fpga_clk,

23     input reset,

24     output clk_50M,

25     output clk_25M,

26     output lock_led

27 );

28

29 dcm_25 instance_name (

30     .CLKIN_IN(fpga_clk), //50MHz xtal clock to FPGA

31     .RST_IN(reset),

32     .CLKDV_OUT(clk_25M), //25MHz clock to VGA controller

33     .CLKIN_IBUFG_OUT(), //Open

34     .CLKO_OUT(clk_50M), //50MHz clkout to rest of design

35     .LOCKED_OUT(lock_led) //LED turns on when DCM is locked

36 );

37

38 endmodule

39

```

The code defines a module 'dcm\_example' with four ports: 'fpga\_clk', 'reset', 'clk\_50M', and 'lock\_led'. It contains an instantiation of a 'dcm\_25' component with various port connections. The code is color-coded for syntax highlighting.

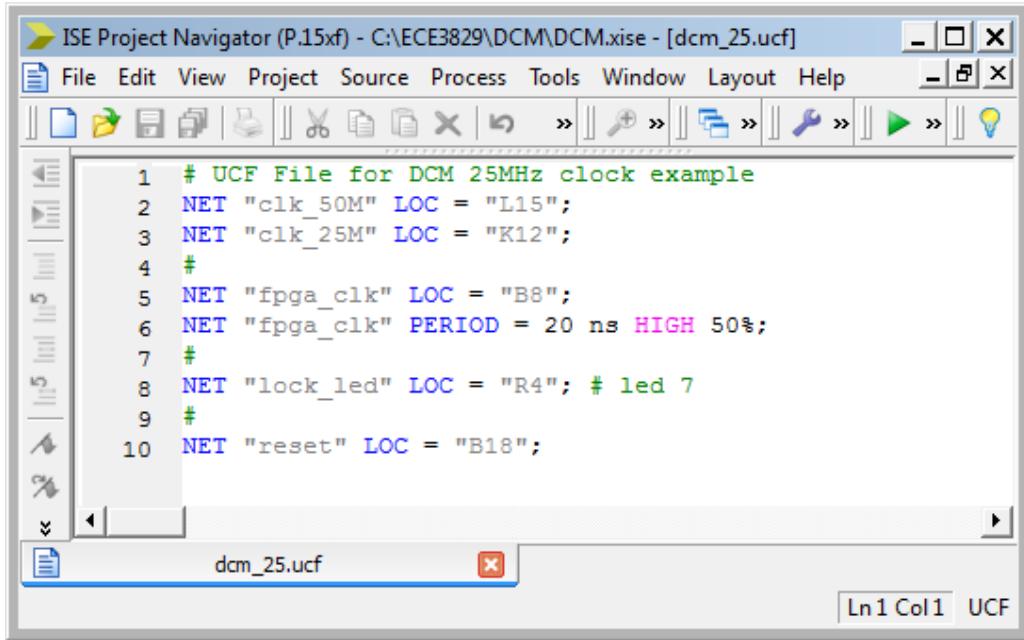

Create a UCF File (clk\_50MHz is connected to debug port JA1, and Clk\_25M to JA2):

```

1 # UCF File for DCM 25MHz clock example

2 NET "clk_50M" LOC = "L15";

3 NET "clk_25M" LOC = "K12";

4 #

5 NET "fpga_clk" LOC = "B8";

6 NET "fpga_clk" PERIOD = 20 ns HIGH 50%;

7 #

8 NET "lock_led" LOC = "R4"; # led 7

9 #

10 NET "reset" LOC = "B18";

```

Synthesize, Implement, and Generate a Programming File,

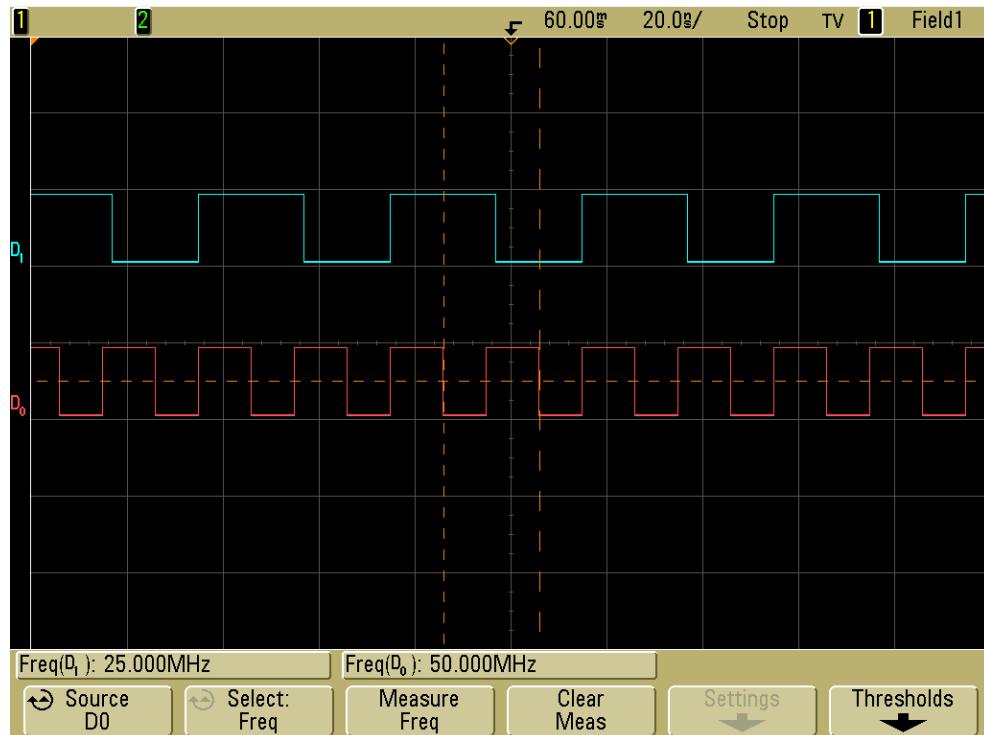

Using an oscilloscope confirm that JA1 has a 50MHz clock and JA2 has a 25MHz clock and the LED 7 is on indicating the DCM is locked.

Press BTN0 to try reset the DCM and confirming the DCM locks again and the clock signals are correct.

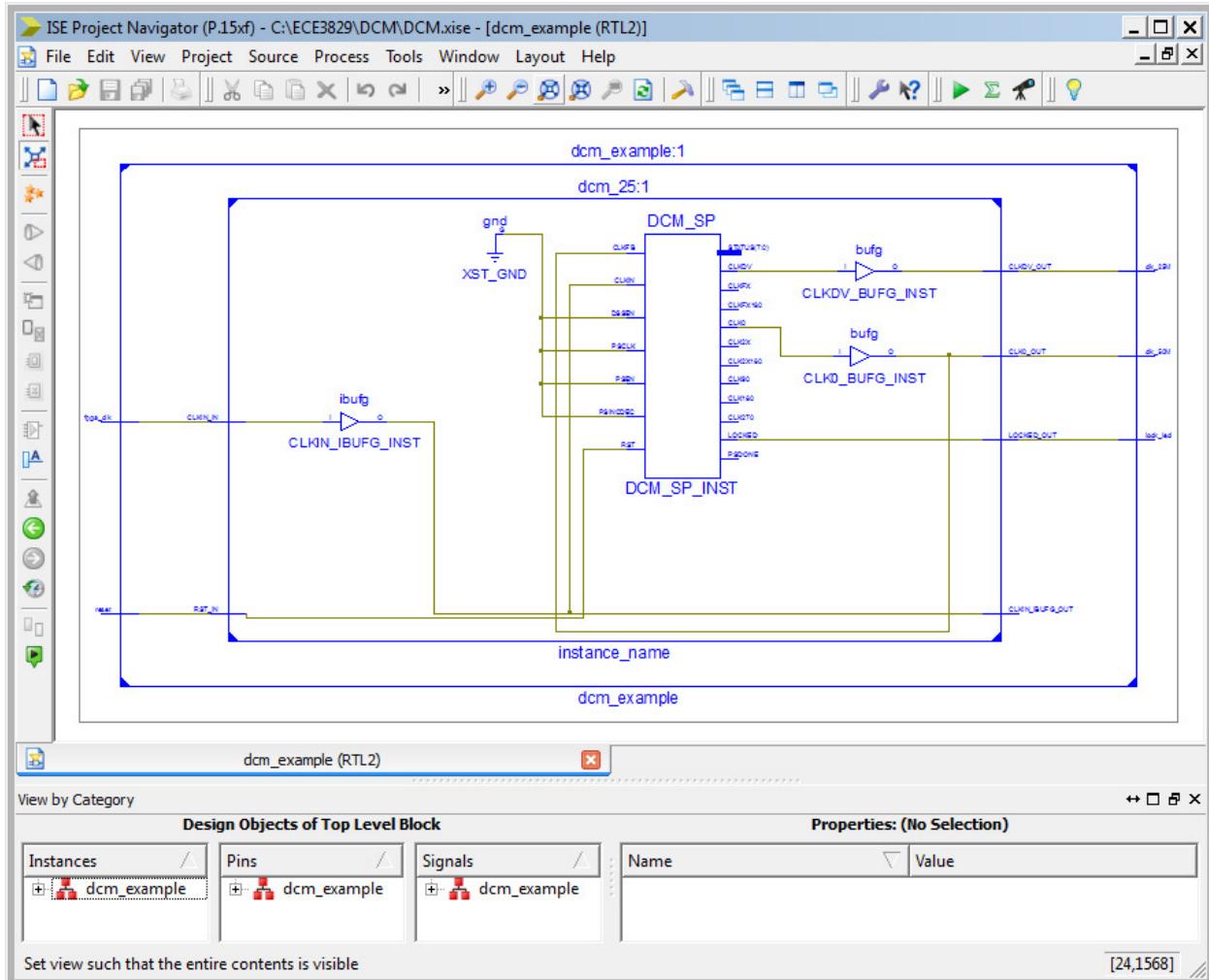

Here is a schematic of what we have created: