# **BOSTON UNIVERSITY**

# **COLLEGE OF ENGINEERING**

# **DISSERTATION**

# JITTER IN RING OSCILLATORS

BY

JOHN ARTHUR McNEILL

A. B., Dartmouth College, 1983

M. S. E. E., University of Rochester, 1991

Submitted in partial fulfillment of the requirements for the degree

Doctor of Philosophy

1994

© Copyright by JOHN ARTHUR McNEILL 1994

# Approved by

| First Reader    |                                               |

|-----------------|-----------------------------------------------|

|                 | Dr. Anton Mavretic                            |

|                 | Associate Professor of Electrical Engineering |

|                 |                                               |

| Second Reader   |                                               |

| 2000110 1100001 | Mr. Lawrence DeVito                           |

|                 | Special Services Appointed Professor          |

|                 |                                               |

| Third Deeden    |                                               |

| Third Reader    | Dr. David Perreault                           |

|                 | Associate Professor of Electrical Engineering |

|                 |                                               |

|                 |                                               |

| Fourth Reader   |                                               |

|                 | Dr. Mark Horenstein                           |

|                 | Associate Professor of Electrical Engineering |

### Acknowledgments

The work in this thesis would not have been possible without many people whose contributions are now acknowledged.

At Analog Devices Semiconductor:

Larry DeVito, Rosamaria Croughwell, and Alex Gusinov, engineers with whom it was a genuine pleasure to work;

Bob Surette, for outstanding support in laboratory measurements;

Tony Freitas, for considerable layout expertise;

Dennis Buss, for all-important financial support;

Maryanne Masterson and Frank Holden for fabrication and trim support;

Bob Adams, Paul Brokaw, Barrie Gilbert, Janos Kovacs, and Chris Mangelsdorf for enlightening conversations.

### At Tektronix:

Scott Casstevens, for providing the CSA803A for high accuracy jitter measurements; Laszlo Dobos, for his insights into jitter.

At Boston University:

Anton Mavretic, for his direction and support;

David Perreault, Mark Horenstein, and Emile Gergin for their time and effort on the dissertation committee;

The faculty and staff, particularly Professor Lev Levitin, graduate coordinators Mike Ruane and Roscoe Giles, Dean William Taft, Chairman Thomas Kincaid, and Director Wayne Rennie.

Most importantly, I thank my family - especially my wife, Kristina - for their love, patience, and support.

### JITTER IN RING OSCILLATORS

(Order No.

### JOHN ARTHUR McNEILL

Boston University, College of Engineering, 1994

Major Professor: Dr. Anton Mavretic,

Associate Professor of Electrical Engineering

### **ABSTRACT**

This thesis describes a methodology for analyzing and predicting jitter (phase noise) in ring oscillators. Due to their high operating frequency and ease of integration, use of rings in jitter sensitive applications is becoming more common. One example is in data communication, where a ring is used as the voltage controlled oscillator (VCO) in a phase-locked loop (PLL). Despite the wide use of ring oscillators, their jitter performance has been poorly understood.

The first step in developing this methodology is a technique for relating various measures of jitter in PLLs. The technique establishes correspondence among time and frequency domain measures of jitter with the PLL loop open or closed. Results are given when this time/frequency technique is applied to jitter measurements from an existing PLL.

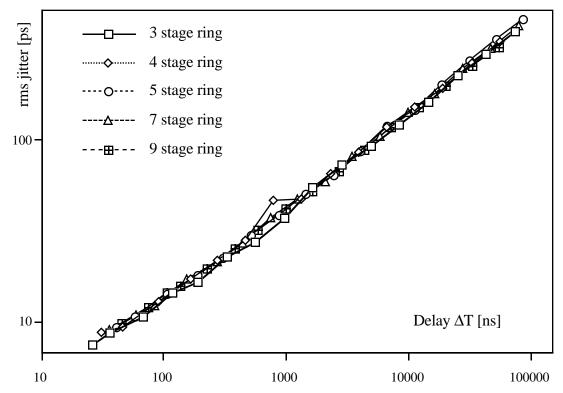

The next step is to determine the fundamental sources of jitter in rings and how they affect the measured performance. A review of analysis techniques for harmonic and relaxation oscillators shows that a different approach is needed to design for low jitter in rings. The approach taken follows naturally from the time/frequency jitter technique developed in the first part of the thesis. A major contribution is the identification of a design figure of merit which is independent of both the ring frequency and number of stages. Experimental results from several rings of different lengths demonstrate that jitter depends primarily on thermal noise sources in the delay stage, and has little to do with the number of stages in the ring.

The final result is a simple design procedure which gives explicit constraints on circuit elements as a function of desired jitter performance. The design of a low jitter ring VCO for a 155 MHz clock recovery PLL is described. Some of the inherent limitations of the

ring architecture, as well as design techniques for dealing with those limitations, are discussed. Test results are presented for the PLL, which has been fabricated in a dielectrically isolated complementary bipolar process.

# **Table of Contents**

| Acknowledgm     | entsiv                                              |

|-----------------|-----------------------------------------------------|

| Abstract        | v                                                   |

| Table of Conte  | entsvii                                             |

| List of Figures | and Tablesxi                                        |

| List of Symbo   | lsxv                                                |

| List of abbrevi | ations and acronymsxviii                            |

|                 |                                                     |

|                 | ı                                                   |

|                 | of this thesis                                      |

|                 | ications                                            |

| 1.1.1           | Clock recovery in serial data transmission          |

| 1.1.2           | Methods of clock recovery6                          |

| 1.1.3           | Other Applications6                                 |

| 1.1.4           | Summary                                             |

| 1.2 Phase       | e and Jitter Concepts in PLL-based Clock Recovery8  |

| 1.2.1           | VCO and phase9                                      |

| 1.2.2           | Response of PLL to input signal and VCO phase noise |

| 1.2.3           | Summary                                             |

| 1.3 Type        | es of VCOs16                                        |

| 1.3.1           | LC/resonant                                         |

| 1.3.2           | Multivibrator                                       |

| 1.3.3           | Ring oscillator                                     |

| 1.3.4           | Summary: Focus on ring oscillator design techniques |

| 1.4 How         | to measure phase                                    |

| 1.4.1           | Phase measures in time and frequency domains        |

| 1.4.2           | Time domain: Two sample standard deviation          |

| 1.4.3           | Other time domain measures                          |

| 1.4.4           | Frequency domain phase measures                     |

| 1.4.5           | Summary                                             |

|                 | sures that will be related in this thesis           |

| 1.5.1         | Case (i): Frequency domain, VCO open loop                             | 26 |

|---------------|-----------------------------------------------------------------------|----|

| 1.5.2         | Case (ii): Frequency domain, VCO closed loop                          | 28 |

| 1.5.3         | Case (iii): Time domain, closed loop, transmit clock ref              | 30 |

| 1.5.4         | Case (iv): Time domain, closed loop, self referenced                  | 32 |

| 1.5.5         | Case (v): Time domain, open loop, self referenced                     | 34 |

| 1.5.6         | Summary                                                               | 36 |

| 1.6 Mo        | tivation and goals of this work                                       | 38 |

| 1.6.1         | Goals                                                                 | 38 |

| 1.6.2         | Other benefits                                                        | 39 |

| 1.6.3         | Summary                                                               | 39 |

| 2. Techniqu   | e for relating time / frequency domain jitter measures                | 40 |

| 2.1 The       | oretical development                                                  | 40 |

| 2.1.1         | Case (i): Frequency domain, VCO open loop                             | 40 |

| 2.1.2         | Case (ii): Frequency domain, PLL closed loop                          | 41 |

| 2.1.3         | Case (iii): Time domain, closed loop, transmit clock ref              | 41 |

| 2.1.4         | Case (iv): Time domain, closed loop, self referenced                  | 42 |

| 2.1.5         | Case (v): Time domain, open loop, self referenced                     | 42 |

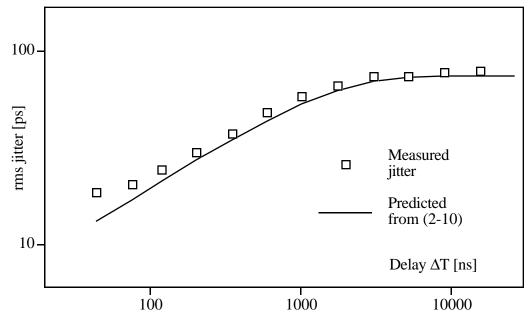

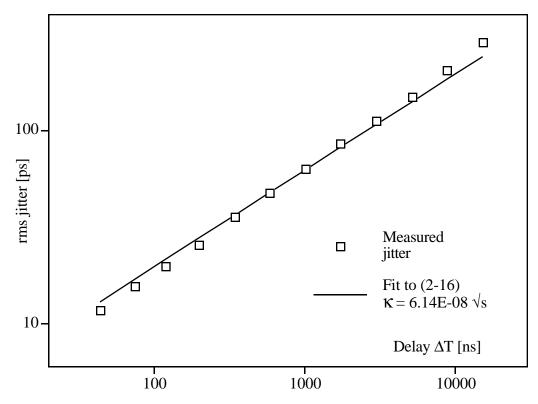

| 2.2 Exp       | perimental verification                                               | 45 |

| 2.2.1         | PLL with multivibrator VCO                                            | 45 |

| 2.2.2         | Ring VCO                                                              | 50 |

| 2.2.3         | Discussion of results                                                 | 53 |

| 2.3 Cha       | pter summary                                                          | 54 |

| 3. Analysis o | f jitter in ring oscillators                                          | 55 |

| 3.1 Revie     | ew of jitter analysis in different types of oscillators               | 55 |

| 3.1.1         | Harmonic oscillators.                                                 | 56 |

| 3.1.2         | Relaxation oscillator                                                 | 60 |

| 3.1.3         | Ring oscillator                                                       | 64 |

| 3.2 Jitter    | model theoretical development                                         | 65 |

| 3.2.1         | Approach                                                              | 65 |

| 3.2.2         | Special case: Independent delay errors give 1/f <sup>2</sup> spectrum | 70 |

| 3.2.3         | General case: Correlated delay errors                                 | 73 |

| 3 2 4         | Simplified procedure for long delay asymptote                         | 77 |

| 3.2.5           | Development in terms of gate delays                      | 79  |

|-----------------|----------------------------------------------------------|-----|

| 3.2.6           | Methodology                                              | 80  |

| 3.3 Apply       | ring model to circuit design                             | 81  |

| 3.3.1           | Sources of jitter in individual delays                   | 81  |

| 3.3.2           | Causes of period-to-period coupling that increase jitter | 84  |

| 3.4 Expe        | erimental verification                                   | 87  |

| 3.5 Chap        | oter summary                                             | 91  |

|                 |                                                          |     |

| 4. Sources of   | itter in ring oscillators                                | 92  |

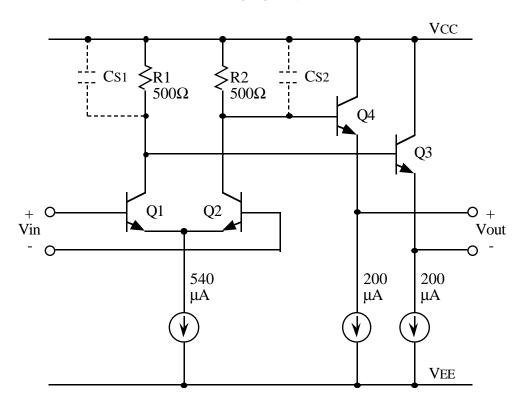

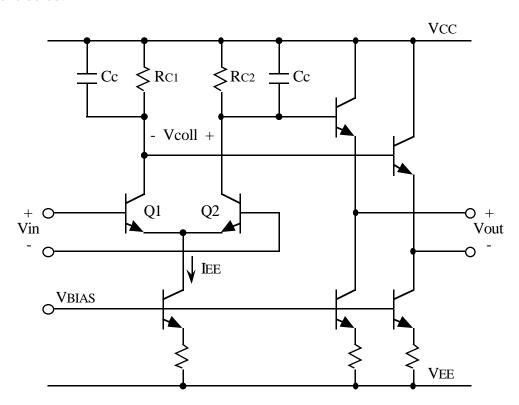

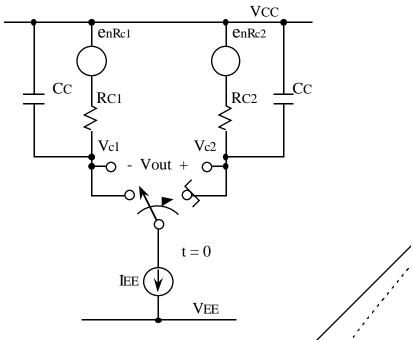

| 4.1 Simpl       | e differential pair                                      | 92  |

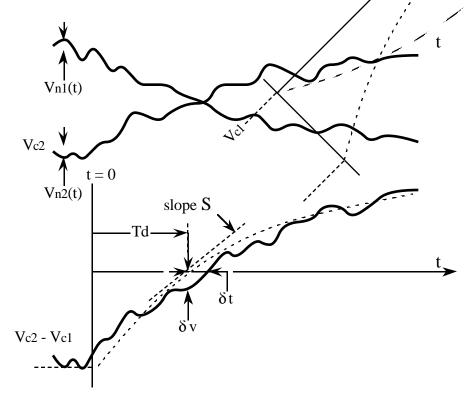

| 4.1.1           | Thermal noise of load resistors                          | 94  |

| 4.1.2           | Tail current noise                                       | 98  |

| 4.1.3           | Switching of input noise                                 | 102 |

| 4.1.4           | Summary of noise contributions                           | 108 |

| 4.2 Expe        | erimental Verification                                   | 110 |

| 4.2.1           | Simulation                                               | 110 |

| 4.2.2           | Hardware tests                                           | 115 |

| 4.3 Impl        | ications for design and simulation                       | 121 |

| 4.4 Com         | parison with jitter in harmonic oscillator               | 124 |

| 4.5 Chap        | oter summary                                             | 128 |

| 5. Design of lo | ow jitter VCO for AD806                                  | 129 |

| 5.1 VCC         | Requirements                                             | 129 |

| 5.1.1           | Low jitter                                               | 129 |

| 5.1.2           | Very low duty cycle distortion                           | 129 |

| 5.1.3           | Quadrature                                               | 129 |

| 5.1.4           | Control constant linearity                               | 130 |

| 5.1.5           | Low power                                                | 130 |

| 5.2 Ring        | oscillator design                                        | 131 |

| 5.2.1           | Development of basic ring                                | 131 |

| 5.2.2           | Drawbacks to the ring oscillator architecture            | 136 |

| 5.2.3           | Improvements to ring oscillator                          | 140 |

| 5.3 Expe        | erimental Results                                        | 145 |

| 5.4 Chap        | oter summary                                             | 153 |

| 6. I | 6. Design procedure                                                |     |

|------|--------------------------------------------------------------------|-----|

|      | 6.1 Step 1: refer design goal to asymptotic <b>K</b>               | 154 |

|      | 6.1.1 Time domain: $\sigma_x$                                      | 154 |

|      | 6.2.2 Frequency domain: N <sub>1</sub>                             | 154 |

|      | 6.2 Step 2: adjust asymptotic <b>K</b> to gate-level <b>K</b>      | 155 |

|      | 6.3 Step 3: determine constraints on the design of individual gate | 156 |

|      | 6.4 Step 4: design for ring center frequency                       | 158 |

|      | 6.5 General design techniques for low jitter                       | 159 |

|      | 6.6 Chapter Summary                                                | 159 |

| 7.   | Summary                                                            | 160 |

| A.   | Approximate loop transfer functions                                | 163 |

| В.   | Power spectra relationships                                        | 166 |

| C.   | Analysis of jitter process                                         | 171 |

| D.   | Data acquisition techniques.                                       | 173 |

| E.   | Stationarity of two-sample variance                                | 178 |

| F.   | Variance of clock period errors                                    | 180 |

| G.   | Exponential waveform coupling                                      | 184 |

| Η.   | Differential pair switching delay                                  | 186 |

| I.   | Time-domain (transient) noise source simulation                    | 189 |

| Re   | ferences                                                           | 193 |

| Vit  | a                                                                  | 204 |

# List of Figures and Tables

| 1.1  | Typical fiber optic serial data transmission system              |

|------|------------------------------------------------------------------|

| 1.2  | Independent test of BER due to clock recovery function           |

| 1.3  | PLL used for clock and data recovery                             |

| 1.4  | Definition of general VCO                                        |

| 1.5  | Ideal free running VCO                                           |

| 1.6  | Free running VCO integrating white noise at input                |

| 1.7  | $1/f^2$ p.s.d. of integrated white noise                         |

| 1.8  | Phaselock loop as a control system                               |

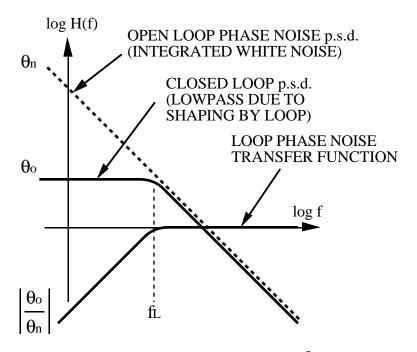

| 1.9  | Phase signal and noise Bode plots                                |

| 1.10 | Lowpass process for shaped 1/f <sup>2</sup> noise                |

| 1.11 | Ideal clock                                                      |

| 1.12 | Clock with phase noise                                           |

| 1.13 | "Direct spectrum" measurement of phase noise                     |

| 1.14 | Jitter measurement over time delay $\Delta T$                    |

| 1.15 | Clock jitter in time and frequency domains                       |

| 1.16 | Measurement technique: Frequency domain, open loop               |

| 1.17 | Measurement result: Frequency domain, open loop                  |

| 1.18 | Measurement technique: Frequency domain, closed loop             |

| 1.19 | Measurement result: Frequency domain, closed loop                |

| 1.20 | Measurement technique: Time domain, closed loop, transmit clock  |

| 1.21 | Measurement result: Time domain, closed loop, transmit clock     |

| 1.22 | Measurement technique: Time domain, closed loop, self referenced |

| 1.23 | Measurement result: Time domain, closed loop, self referenced    |

| 1.24 | Measurement technique: Time domain, open loop, self referenced   |

| 1.25 | Measurement result: Time domain, open loop, self referenced      |

| 1.26 | Summary of jitter measurement techniques                         |

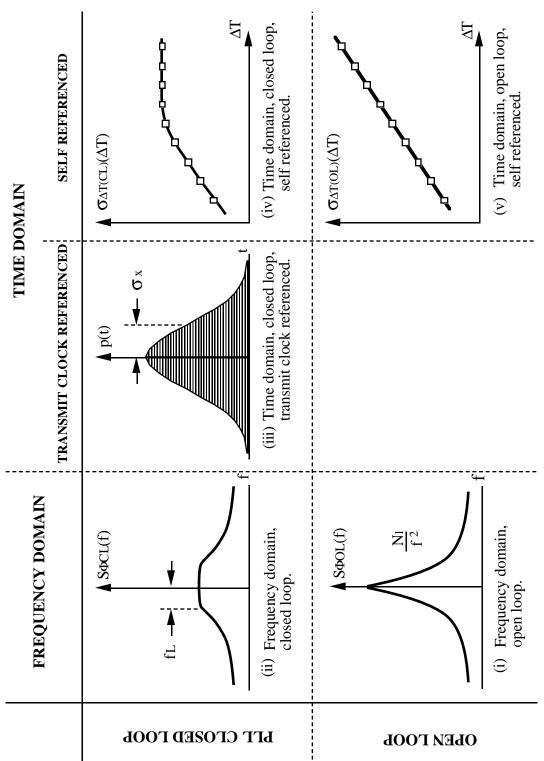

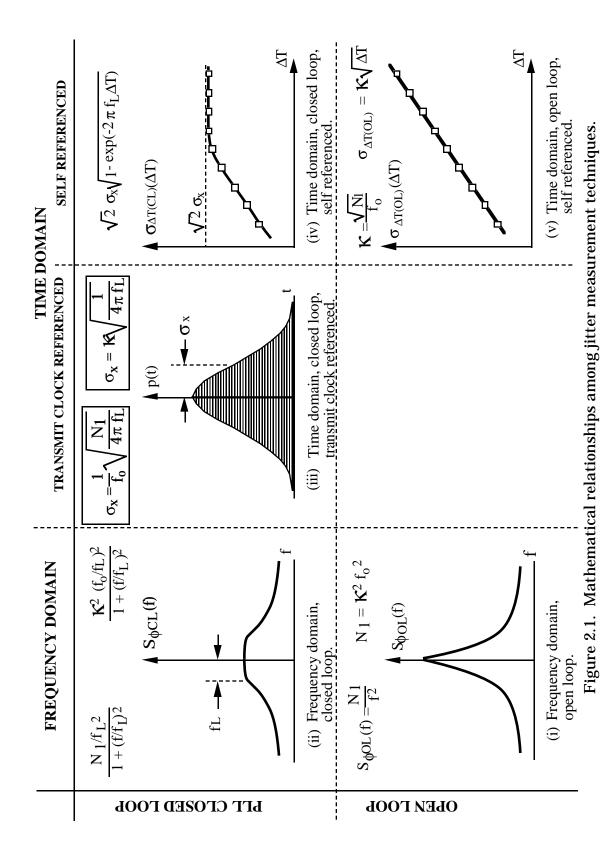

| 2.1  | Mathematical relationships among jitter measurement techniques   |

| 2.2  | AD802: Open loop spectrum                                        |

| 2.3  | AD802: Closed loop spectrum                                      |

| 2 4  | AD802: Time domain, closed loop, transmit clock referenced       |

- 2.5 AD802: Time domain, closed loop, self referenced

2.6 AD802: Time domain, open loop, self referenced

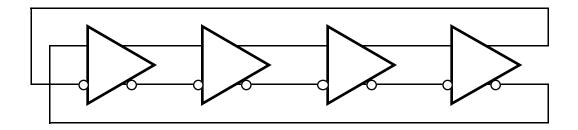

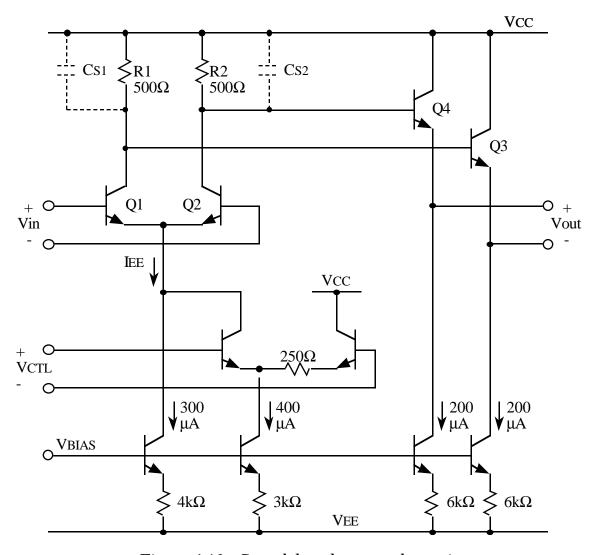

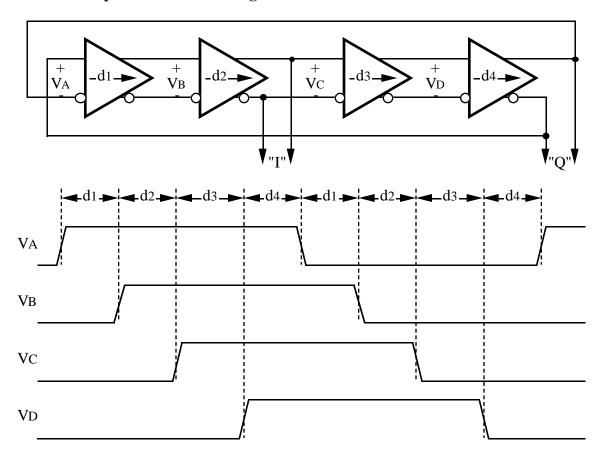

2.7 4 stage ring VCO schematic

- 2.8 4 stage ring VCO: frequency domain, open loop

- 2.9 4 stage ring VCO: time domain, open loop, self referenced

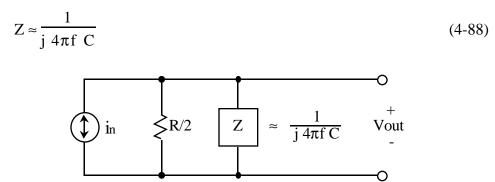

- 3.1 L(R/2)C resonant circuit analyzed by Golay

- 3.2 Impedance of resonant circuit vs. frequency

- 3.3 Classic emitter-coupled multivibrator

- 3.4 Schmitt trigger representations of emitter-coupled multivibrator

- 3.5 Equivalent circuit for noise analysis

- 3.6 Waveforms in multivibrator equivalent circuit

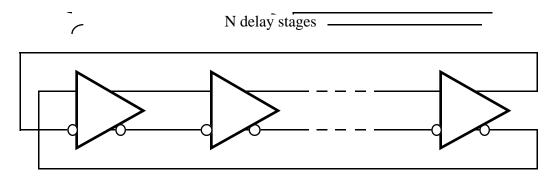

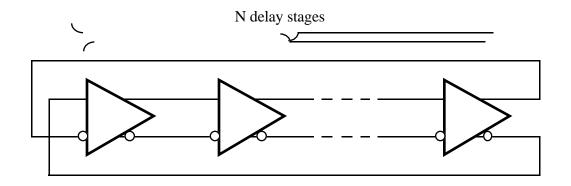

- 3.7 Typical ring oscillator schematic

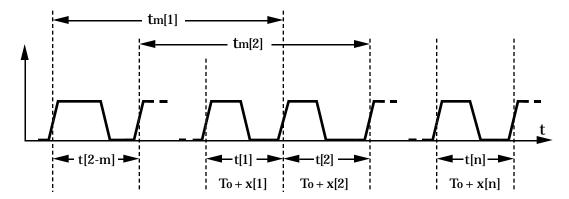

- 3.8 Definition of random processes for clock with jitter

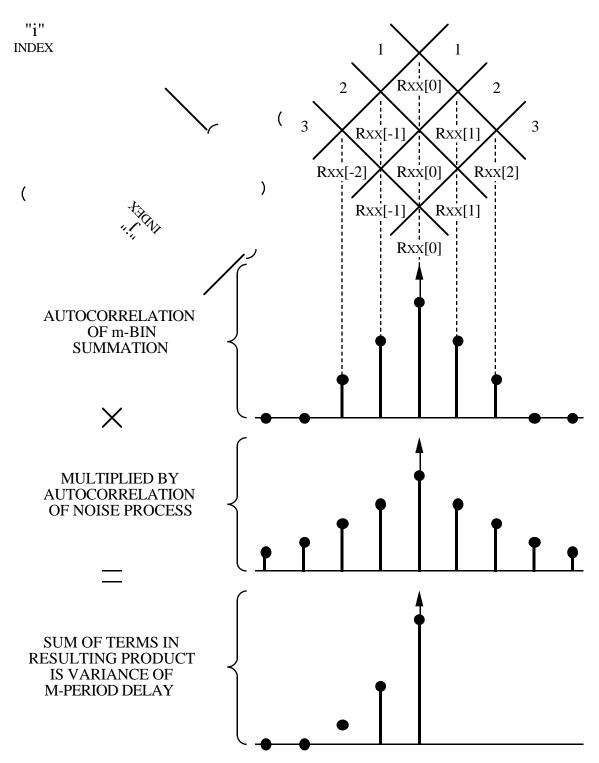

- 3.9 Graphical procedure for autocorrelation calculation

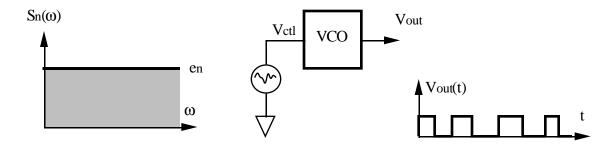

- 3.10 VCO with ideal white noise at input

- 3.11 Autocorrelation of white noise

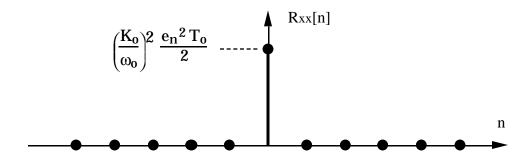

- 3.12 Result of summation procedure for white noise input

- 3.13 VCO with bandlimited white noise at input

- 3.14 Autocorrelation of bandlimited white noise

- 3.15 Result of summation procedure for bandlimited white noise input

- 3.16 Measured jitter with bandlimited white noise at VCO input

- 3.17 Autocorrelation for asymptote example

- 3.18 Ring gate for noise analysis

- 3.19 Noise sources in ring gate

- 3.20 RC waveform with exponential coupling of jitter errors

- 3.21 General schematic for ring experiment

- 3.22 Gate delay element schematic

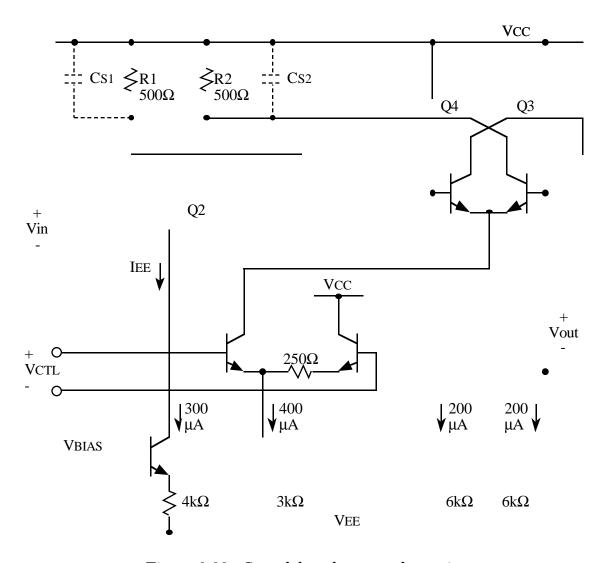

- 3.23 (Table) Ring experiment results

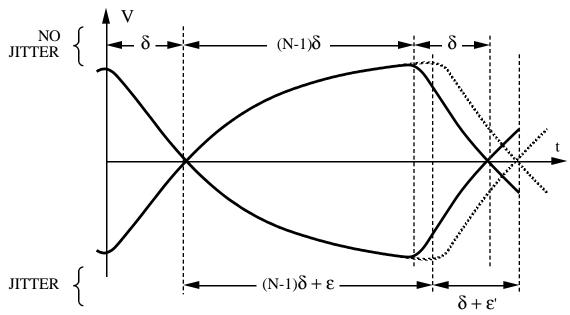

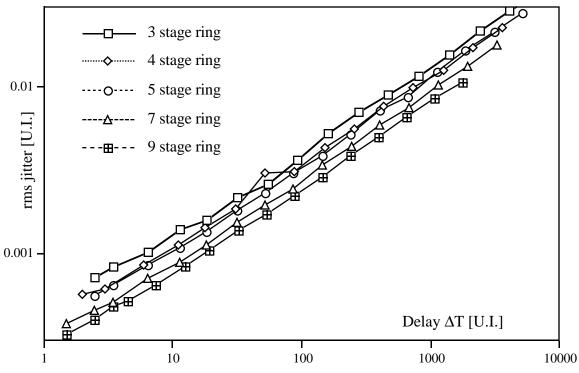

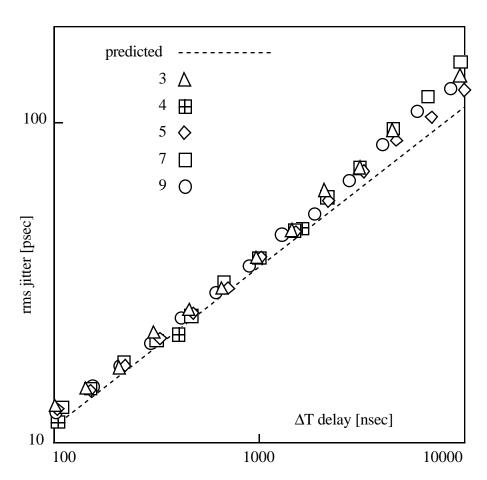

- 3.24 Plot of ring jitter (absolute time) for 3, 4, 5, 7, 9 stage rings

- Plot of ring jitter (normalized time) for 3, 4, 5, 7, 9 stage rings

- 4.1 Differential pair delay gate

- 4.2 Collector resistance thermal noise model

- 4.3 Collector resistance thermal noise waveforms

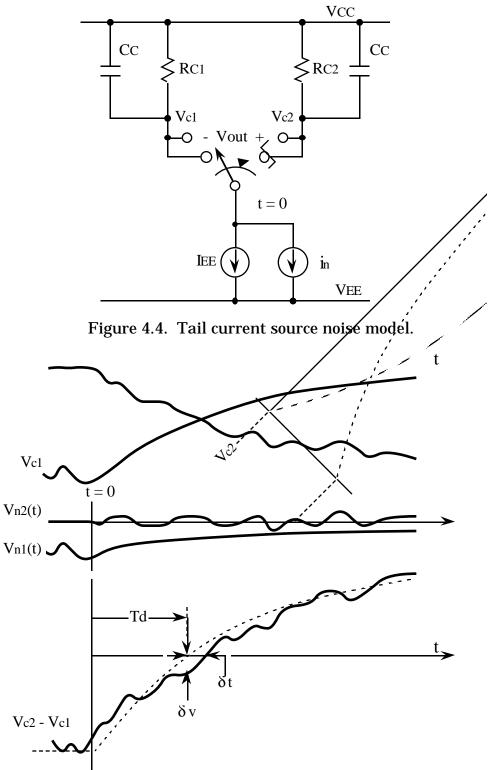

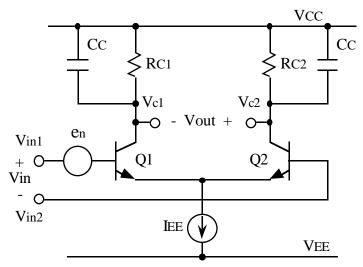

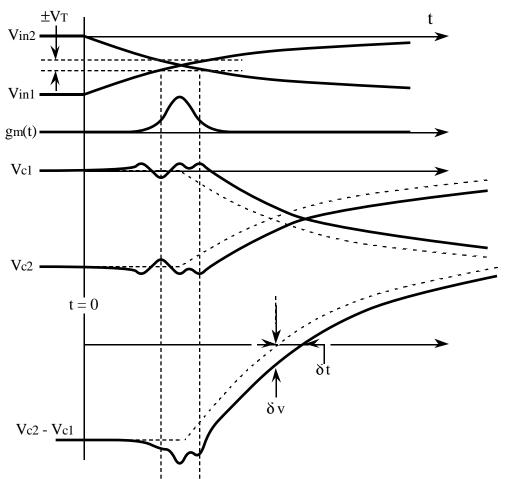

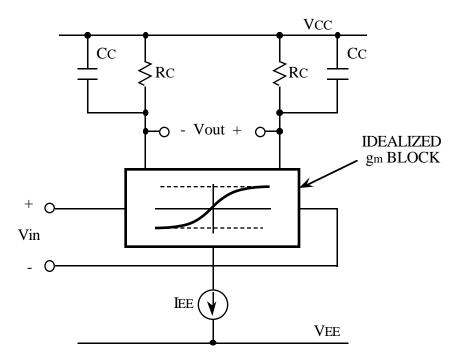

- 4.4 Tail current source noise model

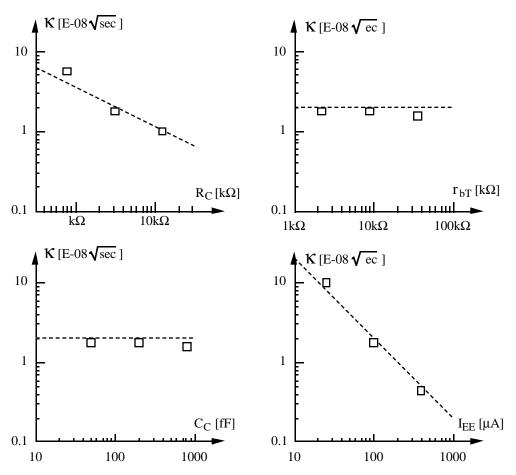

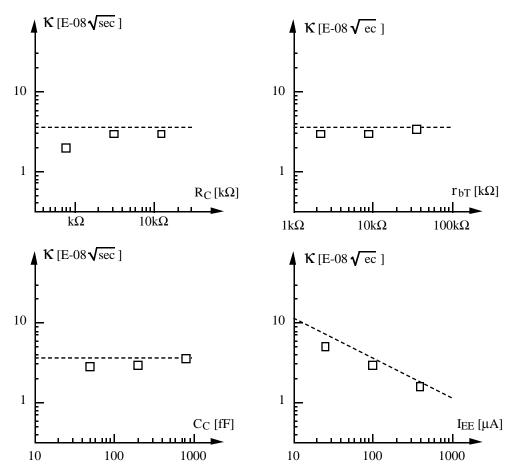

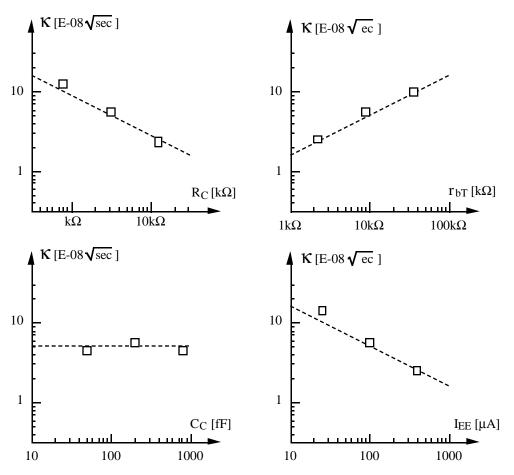

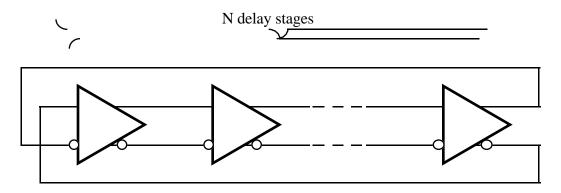

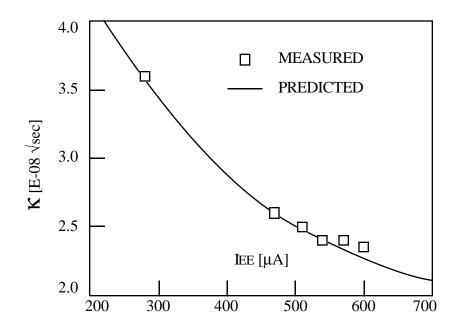

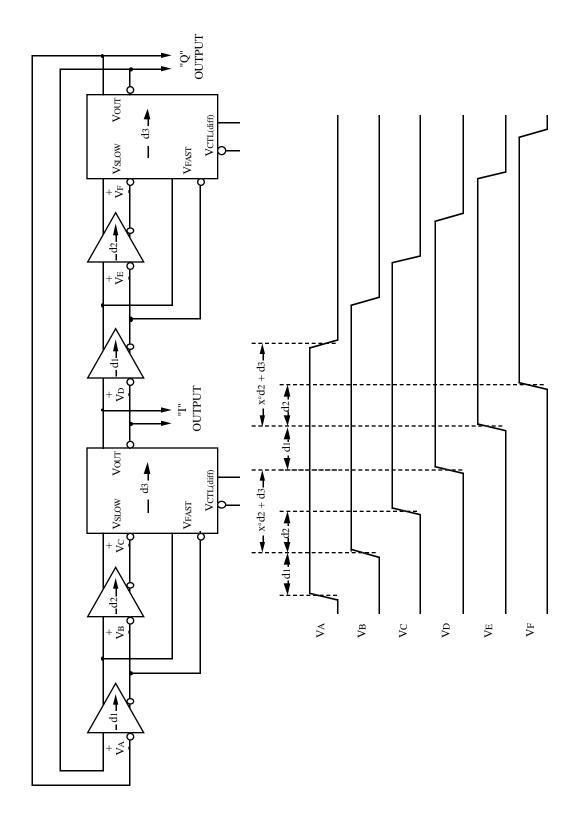

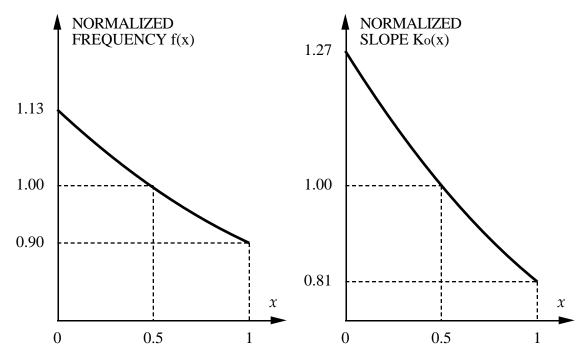

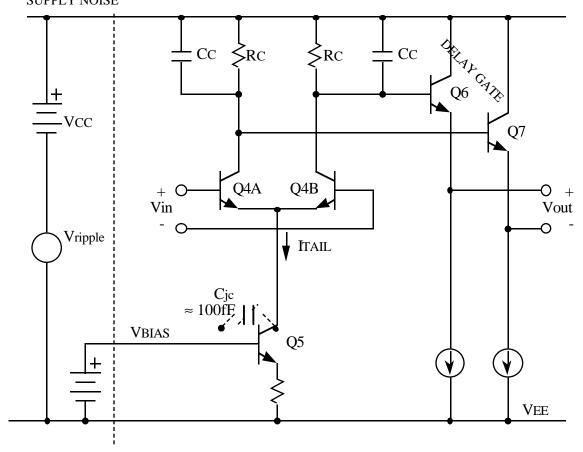

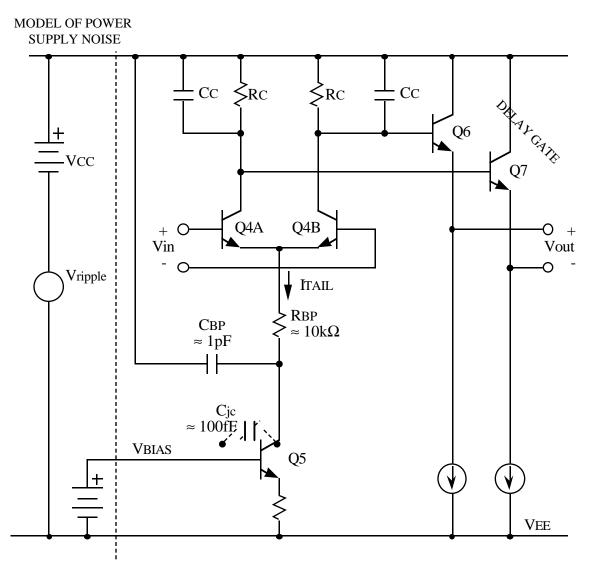

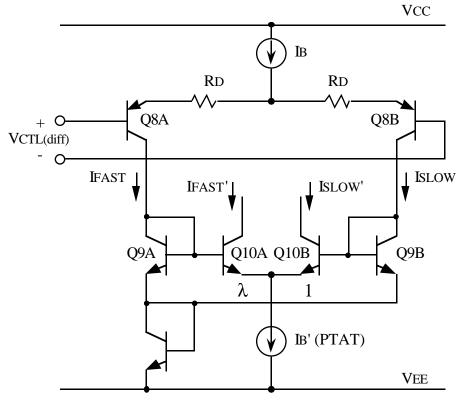

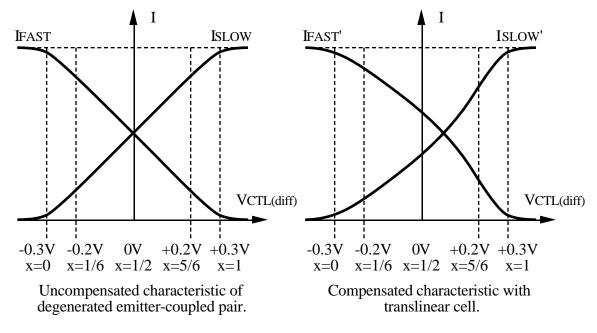

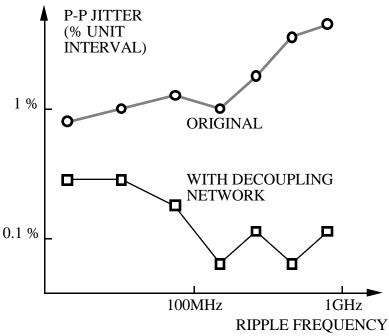

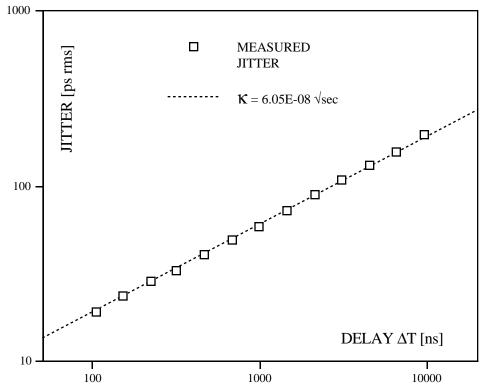

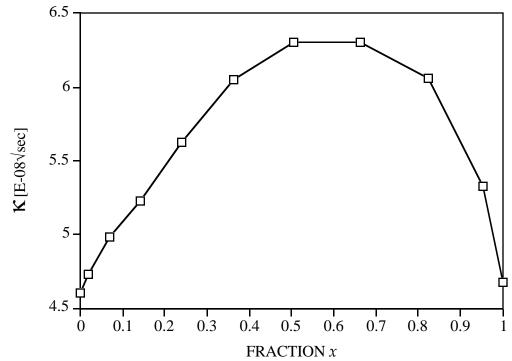

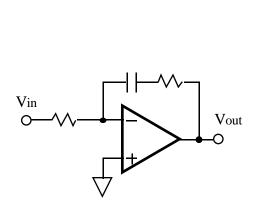

4.5 Tail current source noise waveforms 4.6 Differential input noise switching model 4.7 Differential input noise switching waveforms 4.8 Idealized differential pair for simulation 4.9 (Table) Collector resistance thermal noise simulation results 4.10 Plot of collector resistance thermal noise simulation results 4.11 (Table) Tail current noise simulation results 4.12 Plot of tail current noise simulation results 4.13 (Table) Differential input noise simulation results 4.14 Plot of differential input noise simulation results 4.15 General schematic for ring experiment 4.16 Gate delay element schematic 4.17 (Table) Ring experiment results 4.18 Jitter vs. delay for 3, 4, 5, 7, 9 stage rings 4.19 (Table) Measured results and predicted K vs. I<sub>EE</sub> 4.20 Plot of measured results and predicted K vs. tail current I<sub>EE</sub> 4.21 Noise model of resonator 5.1 4 stage ring schematic 5.2 Interpolating circuit 5.3 Quadrature ring VCO block diagram 5.4 Nonlinearity of interpolating VCO V-to-f characteristic 5.5 Gate schematic with C<sub>ic</sub> stray capacitance 5.6 Gate schematic with bypass network 5.7 Translinear circuit for nonlinearity compensation 5.8 Desired characteristic for linearity compensation 5.9 Simulated V-to-f characteristic, with/without linearity compensation 5.10 Measured VCO linearity 5.11 Simulated center frequency drift over temperature 5.12 Measured temperature drift of frequency 5.13 Simulated supply-induced jitter, with/without decoupling network 5.14 VCO open loop, self referenced jitter 5.15 **K** dependence on VCO interpolation fraction xA.1 Loop filter equivalent circuit A.2 Phase noise transfer function Bode plot

| B.1 | Voltage and phase waveforms with p.s.d.s                       |

|-----|----------------------------------------------------------------|

| B.2 | Representation of phase noise as additive amplitude noise      |

| B.3 | Error integrated by spectrum analyzer                          |

| C.1 | Jitter on clock recovered under closed loop condition          |

| D.1 | Typical time domain measurement program output                 |

| D.2 | Apparent increase in measured $\sigma$                         |

| D.3 | Typical frequency domain measurement program output            |

| E.1 | Definition of x[n] for stationarity proof                      |

| F.1 | Graphical determination of p.s.d. for x[n] process             |

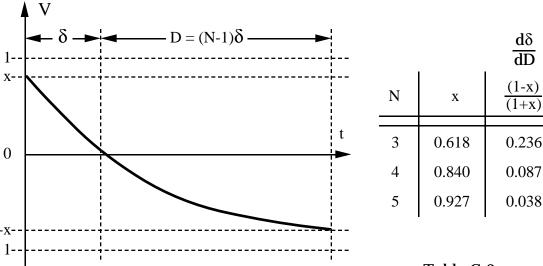

| G.1 | Normalized exponential delay waveform                          |

| G.2 | (Table) Delay coupling as a function of N                      |

| H.1 | Differential pair for switching time calculations              |

| I.1 | Pulsed sample-and-hold waveform for transient noise simulation |

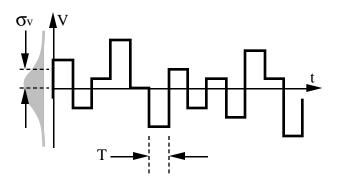

| I.2 | Autocorrelation of pulsed sample-and-hold waveform             |

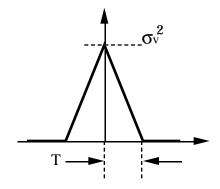

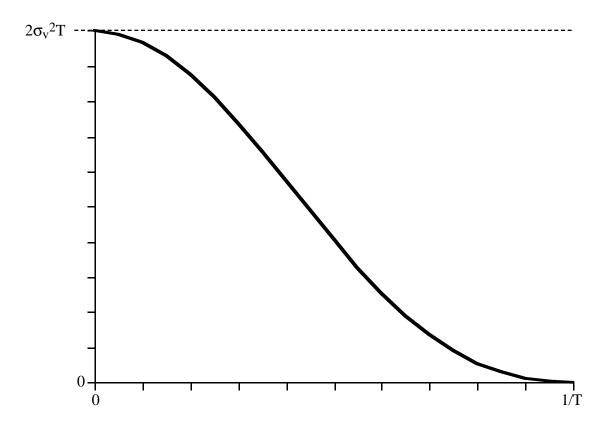

| I.3 | Single-sided p.s.d. of pulsed sample-and-hold waveform         |

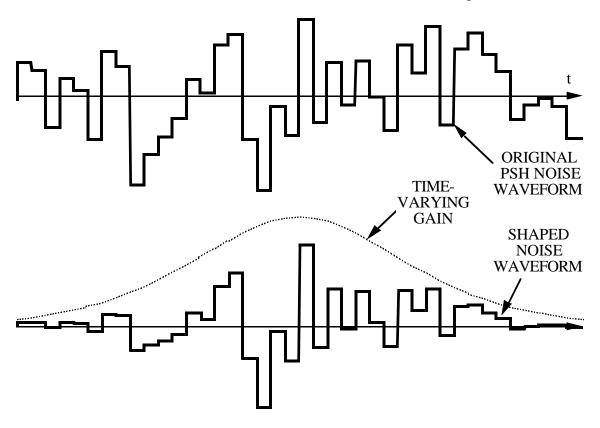

| I.4 | PSH noise waveform shaped by time-varying gain                 |

|     |                                                                |

# List of Symbols

| В                | Noise bandwidth                                       | [Hz]                    |

|------------------|-------------------------------------------------------|-------------------------|

| C                | Capacitance                                           | [F]                     |

| E{}              | Expectation operator                                  |                         |

| $E_{\mathbf{B}}$ | Energy supplied by negative resistor in LC oscillator | [J]                     |

| $e_n$            | Voltage noise density                                 | $[V/\sqrt{H} z]$        |

| f                | Frequency; or "offset" (from carrier) frequency       | [Hz]                    |

| $f_L$            | Loop Bandwidth                                        | [Hz]                    |

| $f_0$            | VCO center frequency                                  | [Hz]                    |

| $f_{out}$        | VCO output frequency                                  | [Hz]                    |

| f(t)             | Frequency modulated over time                         | [Hz]                    |

| $H_n(s)$         | Phase noise transfer function through PLL loop        |                         |

| Hs(s)            | Phase signal transfer function through PLL loop       |                         |

| I                | Current                                               | [A]                     |

| $I_{EE}$         | Differential pair tail current                        | [A]                     |

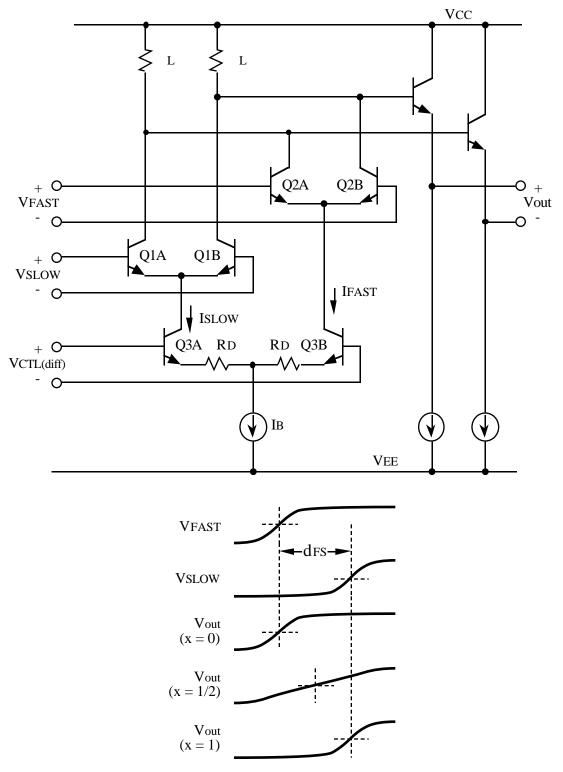

| $I_{FAST}$       | Interpolator current                                  | [A]                     |

| $I_n$            | Noise current                                         | [A]                     |

| $I_{O}$          | DC bias current                                       | [A]                     |

| $I_R$            | Current threshold for regenerative switching          | [A]                     |

| $I_{SLOW}$       | Interpolator current                                  | [A]                     |

| $i_n$            | Current noise density                                 | $[A/\sqrt{H} z]$        |

| j                | $\sqrt{-1}$                                           |                         |

| k                | Boltzmann's constant                                  | [J/K]                   |

| $K_{o}$          | VCO control constant                                  | $[rad/V \cdot s]$       |

| L                | Inductance                                            | [Hy]                    |

| m                | Periods of delay in discrete time process             |                         |

| n                | Index of a discrete time process                      |                         |

| $N_1$            | Open loop frequency domain VCO figure-of-merit        | [rad <sup>2</sup> · Hz] |

| $P_{B}$          | Power flow from negative resistor in LC oscillator    | [J]                     |

| Q                | Quality factor for a second order system              |                         |

| $q_e$            | Electron charge                                       | [coul]                  |

| R                  | Resistance                                               | $[\Omega]$             |

|--------------------|----------------------------------------------------------|------------------------|

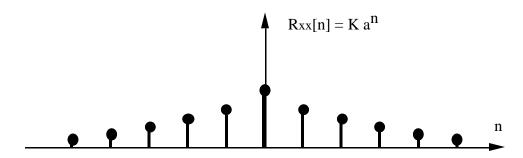

| $R_{xx}(\Delta T)$ | Autocorrelation of the VCO phase jitter process          | [rad <sup>2</sup> ]    |

| S                  | Time derivative (slope) of a waveform                    | [V/s]                  |

| S                  | Laplace complex frequency                                | [rad/s]                |

| $S_{\phi}(f)$      | Phase noise p.s.d.                                       | [rad <sup>2</sup> /Hz] |

| $S_{\phi CL}(f)$   | Closed loop phase noise p.s.d.                           | [rad <sup>2</sup> /Hz] |

| $S_{\phi OL}(f)$   | Open loop phase noise p.s.d.                             | [rad <sup>2</sup> /Hz] |

| t                  | Time                                                     | [s]                    |

| t[n]               | Clock period random process                              |                        |

| t <sub>m</sub> [n] | Random process, sum of m adjacent clock periods          |                        |

| T                  | Temperature                                              | [K]                    |

| $T_d$              | Delay time through a gate                                | [s]                    |

| $T_{o}$            | Period corresponding to center frequency fo              | [s]                    |

| V                  | Voltage                                                  | [V]                    |

| $V_{ctl}$          | VCO input (control) voltage                              | [V]                    |

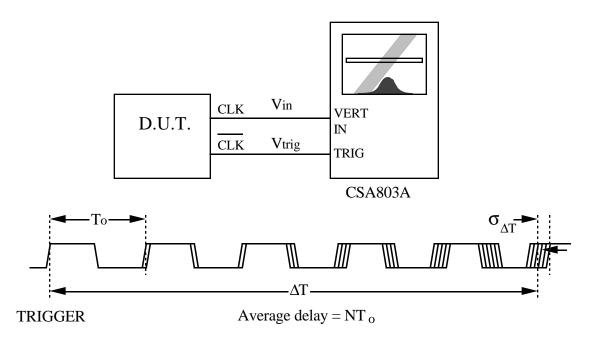

| Vin                | Input voltage (analog representation of serial data)     | [V]                    |

| $V_{trig}$         | Voltage waveform for CSA trigger                         | [V]                    |

| $V_0$              | Voltage amplitude                                        | [V]                    |

| V(t)               | Voltage varying over time                                | [V]                    |

| Y                  | Admittance                                               | [S]                    |

| Z                  | Impedance                                                | $[\Omega]$             |

| α                  | Noise scaling factor (from Abidi and Meyer)              |                        |

| $\delta_t$         | Time error due to noise                                  | [s]                    |

| $\delta_{v}$       | Voltage error due to noise                               | [V]                    |

| $\Delta f$         | rms frequency deviation                                  | [s]                    |

| ΔΤ                 | Delay time for jitter measurement                        | [s]                    |

| ε                  | Gate delay error                                         | [s]                    |

| ζ                  | Damping factor for a second order system                 |                        |

| $\theta_i$         | PLL input phase                                          | [rad]                  |

| $\theta_n$         | PLL phase noise                                          | [rad]                  |

| $\theta_{\rm o}$   | PLL output phase                                         | [rad]                  |

| κ                  | Open-loop time domain VCO figure-of-merit                | $[\sqrt{s}]$           |

| λ                  | Emitter unbalance ratio                                  |                        |

| ρ                  | VCO tuning range (ratio of maximum, minimum frequencies) |                        |

| σ                               | Standard deviation of a distribution                    |         |

|---------------------------------|---------------------------------------------------------|---------|

| $\sigma^2$                      | Variance of a distribution                              |         |

| $\sigma_{t}$                    | Standard deviation of time errors                       | [s]     |

| $\sigma_{v}$                    | Standard deviation of voltage errors                    | [s]     |

| $\sigma_{\scriptscriptstyle X}$ | Closed-loop, transmit-clock-referenced jitter           | [s]     |

| $\sigma_{\Delta T}$             | Self referenced jitter at delay $\Delta T$              | [s]     |

| $\sigma_{\Delta T(CL)}$         | Closed-Loop, self referenced jitter at delay $\Delta T$ | [s]     |

| sDT(OL)                         | Open-Loop, self referenced jitter at delay $\Delta T$   | [s]     |

| $\tau_{T}$                      | Bipolar transistor base transit time                    | [s]     |

| $	au_{ m L}$                    | Time constant associated with loop bandwidth $f_L$      | [s]     |

| ф                               | Phase                                                   | [rad]   |

| $\phi_{\rm O}$                  | Initial phase                                           | [rad]   |

| φ(t)                            | Phase as a function of time ("unwrapped")               | [rad]   |

| ω                               | Angular (natural) frequency                             | [rad/s] |

| $\omega_n$                      | Bandwidth of noise process                              | [rad/s] |

| $\omega_{o}$                    | VCO center frequency                                    | [rad/s] |

| $\omega_{out}$                  | VCO output frequency                                    | [rad/s] |

| $\omega(t)$                     | Natural frequency modulated over time                   | [rad/s] |

# List of abbreviations and acronyms

ATM Asynchronous Transfer Mode

BER Bit Error Rate

CSA Communications Signal Analyzer

FMFrequency Modulation

LTI Linear Time Invariant

NRZ Non-Return to Zero

PLL Phase Locked Loop

PMPhase Modulation

p.s.d. power spectral density

PSH Pulsed Sample and Hold

PTAT Proportional To Absolute Temperature

SONET Synchronous Optical NETwork

UI Unit Interval

VCO Voltage Controlled Oscillator

WSS Wide Sense Stationary

### 1. Introduction

### Structure of this thesis

This thesis is divided into seven chapters. Experimental verification is presented in the same chapter as the corresponding theoretical development, rather than being isolated in a separate chapter.

Section 1.1 of this first chapter introduces the use of PLLs for clock recovery in serial data communication, the main application for which this work was done. Other applications which are concerned with jitter are also mentioned. Section 1.2 introduces fundamental concepts for understanding phase, phase noise, and jitter, as well as their effect on the PLL. Section 1.3 introduces the different types of VCOs that are used in clock recovery PLLs. Section 1.4 is a general introduction to phase and jitter measurement techniques; Section 1.5 is a detailed specification of five jitter measures with which this thesis will be concerned. Section 1.6 establishes the motivation and goals for the work of this thesis and the value of its contributions.

Chapter 2 covers the mathematical development of a technique for relating the five jitter measures of Section 1.5. The technique is verified experimentally through measurements made on several existing PLLs and VCOs in both closed loop and open loop conditions.

Chapter 3 develops a general theoretical approach for analyzing and predicting jitter in ring oscillators. Section 3.1 reviews published jitter analysis techniques for the harmonic oscillator and the multivibrator. This review shows that neither analysis technique by itself is well suited to ring oscillators. Section 3.2 develops a methodology for analyzing jitter in rings. The methodology flows naturally from the time/frequency technique developed in Chapter 2. A major contribution is the identification of a design figure of merit which is independent of both the ring frequency and number of stages. This leads to a simple, general design methodology which is described in Section 3.3. Section 3.4 presents experimental verification of the concepts underlying the methodology.

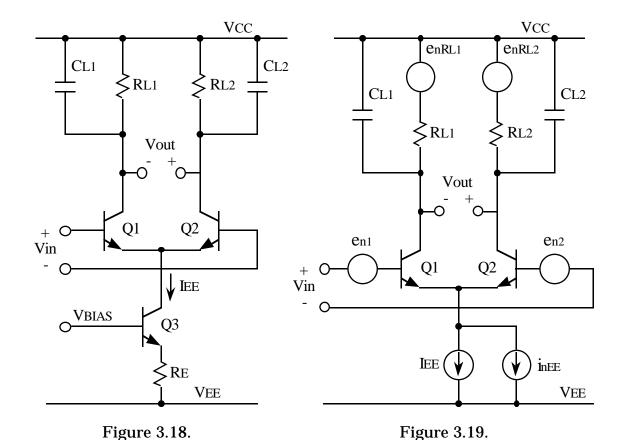

Chapter 4 examines the jitter methodology applied to the detailed design of a ring oscillator composed of differential pair delay stages. This type of ring oscillator is commonly used at high frequencies when low jitter performance is desired. Explicit numerical relationships are developed relating noise sources to resulting jitter.

Experimental results from several rings of different lengths demonstrate the general applicability of this approach.

As an example of the procedure, the design of a low jitter ring VCO for a 155 MHz clock recovery PLL is described in Chapter 5. Some of the inherent limitations of the ring architecture, as well as design techniques for dealing with those limitations, are discussed. The PLL has been fabricated in a dielectrically isolated, complementary bipolar, 5 GHz-f $_T$  (npn) / 4 GHz-f $_T$  (pnp) process. Test results are presented which show good agreement to the design methodology's numerical predictions.

Chapter 6 is a summary for the designer whose interest is applying the methodology to design a low jitter ring oscillator. Starting with desired jitter performance, expressed in either the time or frequency domain, the procedure gives explicit constraints on values of circuit elements.

Chapter 7 concludes by summarizing the developments and contributions of the thesis, and pointing out possible areas for future work.

### 1.1 Applications

### 1.1.1 Clock recovery in serial data transmission

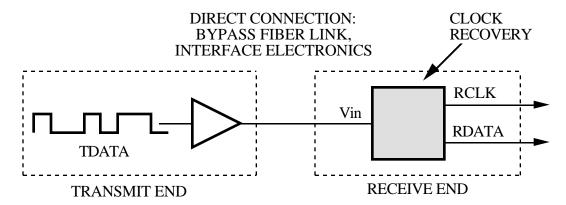

The main application for which this work was originally done is serial data transmission over a fiber optic link. One example is the AT&T Synchronous Optical Network (SONET) standard [102]; another is the emerging Asynchronous Transfer Mode (ATM) protocol [103]. This kind of system is shown conceptually in Figure 1.1. To reduce interconnection hardware, only the data is transmitted over a single fiber. At the receiving end of the link, a clock recovery circuit generates the bit clock RCLK from the serial data stream  $V_{\rm in}$ . The clock recovery circuit also samples  $V_{\rm in}$  to retime the serial data with respect to the recovered clock.

For this application, the ultimate goal of this thesis is to determine how well we can perform the clock recovery function. The timing diagram in Figure 1.1 shows the ideal case when clock recovery is performed perfectly: There is no phase error in the recovered clock, and RCLK samples  $V_{in}$  at the exact center of the bit period. This gives the minimum bit error rate (BER). Any deviation of RCLK from the ideal will increase BER.

In reality, there will be both static ("phase offset") and dynamic ("phase jitter" or simply "jitter") phase errors in the recovered clock, which will degrade performance and increase the BER. Reducing the bit error rate is a major motivation for reducing jitter in the recovered clock. This thesis will address techniques for reducing dynamic phase errors; static phase errors are not considered.

Increased BER is not the only negative effect of jitter in serial data communication. In a repeatered system, where the recovered clock is also used as a transmit clock for a subsequent data link, phase jitter reduces the number of links that can be cascaded before jitter becomes unacceptably large [82].

# TRANSMIT END TDATA TCLK FIBER LINK CLOCK RECOVERY **RECEIVE END RCLK** Vin **RDATA** Vin **RCLK**

Figure 1.1. Typical fiber optic serial data transmission system

**RDATA**

In evaluating the BER performance of a data link, the end user must be concerned with many other possible influences on BER. Among other factors that can degrade system BER in a fiberoptic link are power loss and dispersion in the optical fiber, inadequate optical power input at the transmit end, and noisy optical-to-electronic conversion at the receive end.

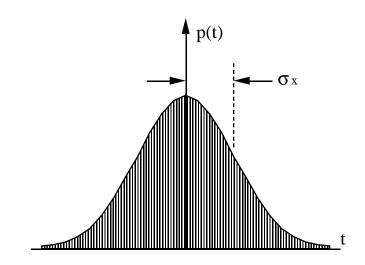

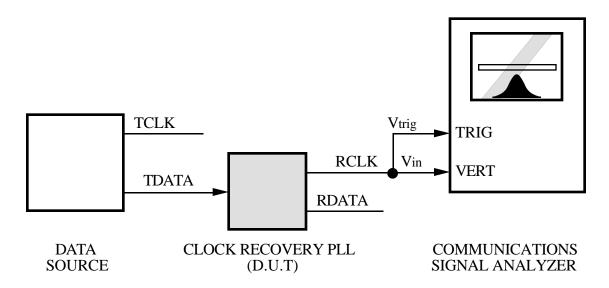

To assess its contribution to BER, the clock recovery block can be tested independent of the link, as shown in Figure 1.2. The input is an ideal data waveform; the recovered clock is then compared to the transmit clock. If there were no jitter, the phase difference between the clocks would be constant (due only to static phase and propagation delay differences). In the presence of jitter, there is a distribution of phase differences. The standard deviation of this distribution  $\sigma_x$  is the end user's figure-of-merit for characterizing the jitter performance of the clock recovery block [93].

Figure 1.2. Independent test of BER due to clock recovery function.

### 1.1.2 Methods of clock recovery

One method of recovering the bit clock is to apply the nonlinearly processed data waveform to a resonant circuit such as a surface acoustic wave (SAW) filter [13, 56]. Nonlinear processing is required since a non-return-to-zero (NRZ) data waveform has a spectral null at the bit frequency [60]. The disadvantage of this approach is that SAW filters are bulky (cannot be integrated) and expensive (of order \$100).

An alternative approach for generating the recovered clock is to use a phase-locked loop (PLL) [13, 20, 58, 81]. This has the advantage of being integrable, and thus relatively inexpensive. This thesis will address design techniques for low jitter performance when a PLL is used for the clock recovery function.

The PLL that was the starting point for this work is the Analog Devices AD802. This PLL is designed for data reception at a frequency of 155.52 MHz. The jitter  $\sigma_x$  for transmission of pseudorandom data is approximately 50ps rms [93]. This is approximately 0.8% of a unit interval (UI).

# 1.1.3 Other Applications

Although this work was done with serial data transmission in mind, there are several other applications requiring low jitter performance from PLLs that perform a clock recovery function:

### Disk drive clock recovery

Data is usually stored on magnetic media with no reference track to indicate bit boundaries. Therefore when data is read from the magnetic medium, there is a need to recover a clock signal from the data to determine the bit boundaries. (Encoding the data makes the clock recovery task somewhat easier than the NRZ data case). Low jitter is necessary since any increase in jitter increases read errors [53, 55, 59].

### Generating high speed digital clocks on-chip

As digital processor and memory chips become capable of operating at clock rates exceeding 100 MHz, the problem of distributing such a high speed clock throughout a system becomes more difficult. One approach to solving this problem is to distribute a lower frequency clock, and multiply this clock to the higher frequency with an on-chip PLL [25, 36, 39, 40, 92]. Low jitter is necessary since any increase in jitter reduces timing margin for digital signals that rely on the clock.

### Digital Audio

A PLL can be used to generate the high-speed clock required for delta-sigma A/D and D/A conversion in digital audio applications. Low jitter is necessary since phase noise on the clock can be aliased into the audio band to produce audible, objectionable artifacts in the reconstructed analog waveform [34, 35].

# **1.1.4 Summary**

Many applications require low jitter PLL performance, characterized by the standard deviation of phase errors in the recovered clock  $\sigma_x$ . The work in this thesis grew out of the need to develop tools for low jitter PLL design, while always being able to relate jitter performance to the end user's figure of merit  $\sigma_x$ .

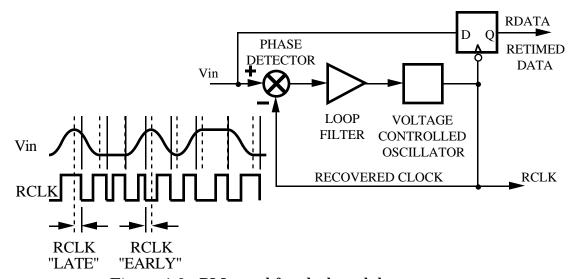

# 1.2 Phase and Jitter Concepts in PLL-based Clock Recovery

Figure 1.3 is a simplified block diagram of a PLL being used for clock recovery. The VCO generates the recovered clock RCLK. The phase detector compares transitions of RCLK to transitions of  $V_{in}$ , and generates an error signal proportional to the phase difference. The error signal is processed by the loop filter and applied to the VCO to drive the phase difference to zero. Ideally there is no phase error, and RCLK samples  $V_{in}$  at the exact center of the bit period, giving the minimum bit error rate.

Figure 1.3. PLL used for clock and data recovery.

Any of the PLL components shown in Figure 1.3 can contribute to jitter [27, 43]. For example, design steps must be taken to ensure that the phase detector does not add data-dependent jitter [20]. When the phase detector and loop filter designs are optimized for low jitter, the remaining source of jitter is the VCO. The goal of this thesis is to achieve low jitter PLL performance by developing techniques for low jitter VCO design.

### 1.2.1 VCO and phase

Phase is simply a number - an angle - the argument of a trigonometric function. For example, in the case of an ideal sine waveform of amplitude  $V_{\text{O}}$  with constant frequency  $\omega$ :

$$V(t) = V_0 \sin (\omega t + \phi_0)$$

PHASE (1-1)

Phase is simply the argument of the sine function,  $\omega t + \phi_0$ . Angle  $\phi_0$  is an initial phase at the (arbitrary) time t=0.

Frequency is simply the time derivative of phase: that is, the rate at which phase changes with time. Conversely, phase is the integral of frequency. For example, in the case where frequency varies in time:

$$\phi(t) = \int_{0}^{t} \omega(t)dt + \phi_{0}$$

(1-2)

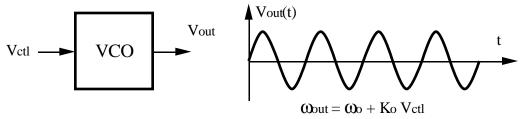

A general VCO may be defined as shown in Figure 1.4. The input voltage  $V_{ctl}$  controls the output frequency  $\omega_{out}$ , which is given by

$$\omega_{\text{out}} = \omega_0 + K_0 \cdot V_{\text{ctl}} \tag{1-3}$$

where  $\omega_o$  is the center frequency and  $K_o$  is the voltage-to-frequency conversion constant (in units of rad/V·s).

Since phase is the integral of frequency, the phase at the VCO output can be obtained by integrating (1-3). Assuming the arbitrary initial phase  $\phi_0$  to be zero, substituting (1-3) into (1-2) gives

$$\phi(t) = \int_{0}^{t} \omega_{\text{out}}(t) dt = \omega_{\text{o}}t + K_{\text{o}} \int_{0}^{t} V_{\text{ctl}} dt$$

(1-4)

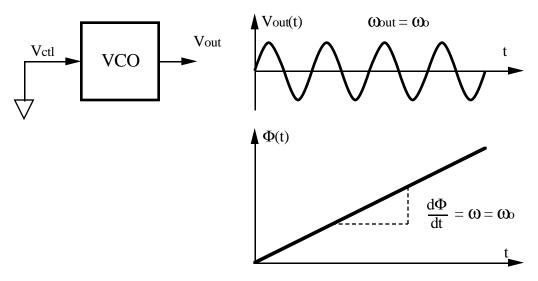

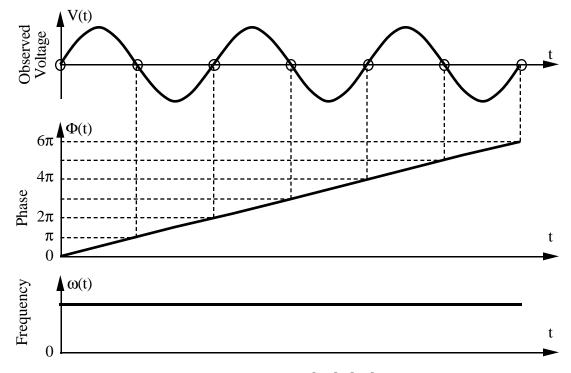

For example, consider the phase at the output of a free-running VCO with zero input, shown in Figure 1.5. The VCO runs at its center frequency  $\omega_0$ , and phase increases uniformly in time as  $\omega_0 t$ .

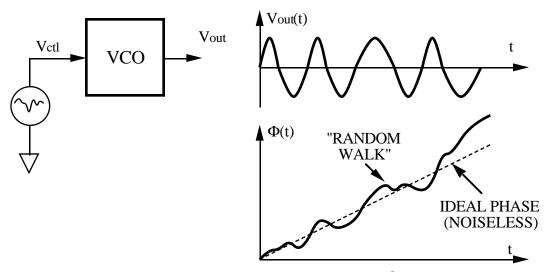

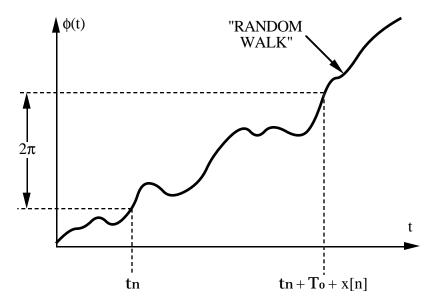

Now consider the case of Figure 1.6, where there is a white noise source at the VCO input. The phase at the VCO output is the integral of the white noise.

Figure 1.4. Definition of general VCO.

Figure 1.5. Ideal free running VCO.

Figure 1.6. Free running VCO integrating white noise at input, giving "random walk" in phase.

As shown in the figure, the output phase executes a "random walk" about the ideal phase  $\omega_0 t$ . The variance of this random walk increases with time, which means that the phase noise at the VCO output is nonstationary. In fact, the integration of frequency to get phase is perfect: over time there is no limit on the phase error.

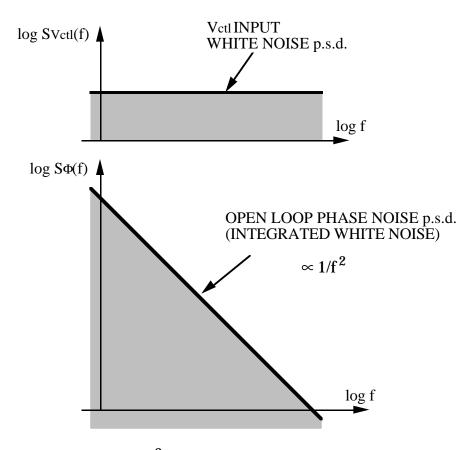

Figure 1.7.  $1/f^2$  p.s.d. of integrated white noise.

Figure 1.7 shows how this nonstationarity is manifest in the (single sided) frequency domain. A white noise power spectrum is integrated to give an output phase power spectrum proportional to  $1/f^2$ . This nonstationarity prevents us from straightforwardly using the usual transform tools to move between the time and frequency domains. Any integral of phase noise power over all frequencies (zero to infinity) diverges due to the infinite power at zero frequency.

### 1.2.2 Response of PLL loop to input signal and VCO phase noise

Most work on phase noise in PLLs assumes that the dominant noise source is the poor signal-to-noise ratio at the PLL input [26, 27]. This is generally <u>not</u> the case in the applications we are concerned about. Usually a comparator is used to improve the amplitude resolution of the input signal threshold crossings. Therefore the signal-to-noise ratio at the PLL input is quite good and has little or no effect on jitter.

In this thesis we will assume that *the dominant source of jitter is the VCO*. Therefore we must be concerned with the phase transfer function from the VCO to the clock output. Following is a brief analysis of phase noise at the output due to the VCO.

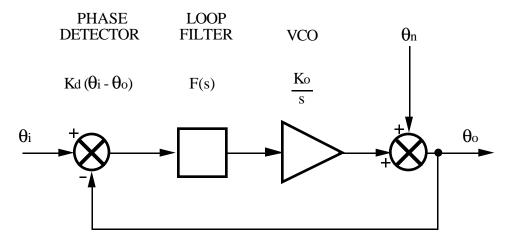

Figure 1.8. Phaselock loop as a control system.

Figure 1.8 shows a block diagram of the PLL as a control system, where the controlled variable is phase.  $\theta_i$  is the input phase from the transmit clock that the PLL is trying to track.  $\theta_0$  is the phase of the VCO output clock.  $\theta_n$  represents the phase noise of the VCO referred to its output.  $K_d$  is the phase detector transfer function, in [V/rad].  $K_o$  is the VCO transfer function, in [rad/V·s].

The signal transfer function  $H_s(s)$  from  $\theta_i$  to  $\theta_0$  is

$$H_{s}(s) = \frac{\theta_{o}}{\theta_{i}} = \frac{K_{d} K_{o} F(s)}{s + K_{d} K_{o} F(s)}$$

(1-5)

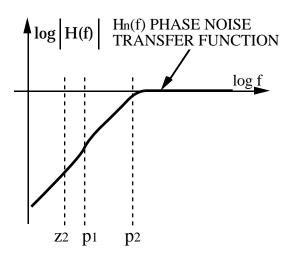

The VCO output-referred phase noise transfer function  $H_n(s)$  from  $\theta_n$  to  $\theta_O$  is

$$H_{n}(s) = \frac{\theta_{O}}{\theta_{n}} = \frac{s}{s + K_{d} K_{O} F(s)}$$

(1-6)

The loop filter usually consists of an integrator and a compensating zero [60]. After considering the effects of the loop filter (see Appendix A), the transfer functions (1-5) and (1-6) can be approximated as

$$H_{s}(s) = \frac{2\pi f_{L}}{s + 2\pi f_{L}} \tag{1-7}$$

$$H_{n}(s) = \frac{s}{s + 2\pi f_{L}} \tag{1-8}$$

where f<sub>L</sub> is the loop bandwidth.

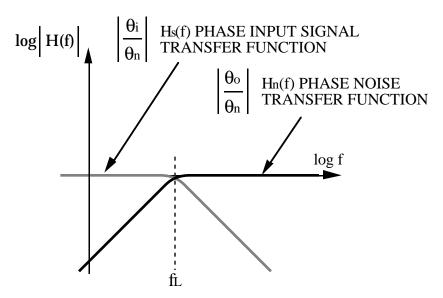

Figure 1.9 shows Bode plots of (1-7) and (1-8), which show the qualitative significance of the loop bandwidth  $f_L$ : The output phase of the PLL is able to follow input phase fluctuations that occur at a frequencies below  $f_L$ ; input phase fluctuations at frequencies above  $f_L$  are attenuated at the output. Conversely, VCO phase noise that occurs at frequencies below  $f_L$  are attenuated at the output; VCO phase noise that fluctuates at frequencies above  $f_L$  are not affected by the loop and pass unattenuated to the output.

As mentioned in Section 1.2.1,  $\theta_n$  can be represented by integrated white noise. When this is passed through the loop filter, the resulting power spectrum is the lowpass noise process shown in Figure 1.10.

Although the open loop VCO noise process is nonstationary, the process at the output of the closed loop VCO is stationary, due to shaping of the noise by the feedback loop. This means transform techniques can be used when the PLL loop is closed.

Figure 1.9. Phase signal and noise Bode plots.

Figure 1.10. Lowpass process for shaped  $1^{/2}$  noise.

For closed-loop operation, the work in this thesis assumes that the PLL has already completed the acquisition process and characterization as a linear system about an operating point is valid. In reality, acquisition is an extremely nonlinear process and must be aided by functional blocks (e.g. a frequency lock loop [20]) not shown in Figure 1.3. This assumption does not limit applicability of the results since jitter is not defined during acquisition.

The work in this thesis also assumes that *cycle slips never occur*. Cycle slips are a more "pathological" nonstationarity than 1/f<sup>2</sup> noise, and make analysis extremely difficult if not impossible [26, 51]. Ignoring cycle slips does not limit applicability of the results since:

- Cycle slips are very rare when jitter is small compared to a bit interval, which is true in this case, and

- Data transmission is in discrete packets so a cycle slip error corrupts only a finite amount of data; the error can be detected and is not fatal.

### **1.2.3 Summary**

In this thesis, we assume the VCO is dominant jitter source. An open loop VCO is a perfect phase integrator, so white noise at the voltage control input is integrated to give a nonstationary "random walk" in phase with a  $1/f^2$  p.s.d. The usual transform tools cannot be applied to the open loop VCO.

When the loop is closed, we assume that acquisition is complete so a linearized loop model is valid. The action of the closed loop shapes the  $1/f^2$  p.s.d., rolling it off below the loop bandwidth  $f_L$ . The shaped noise is stationary and transform tools may be used.

Cycle slips are not addressed in this thesis, but this is not a serious limitation on the applicability of the results.

### 1.3 Types of VCOs

This section briefly describes different types of VCOs that are used in clock recovery PLLs. They will be discussed in detail in Chapter 3.

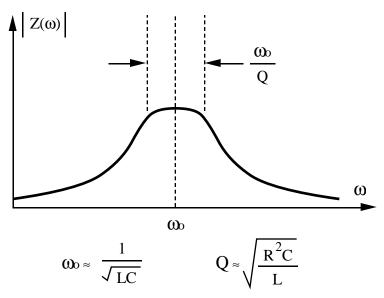

### 1.3.1 LC/resonant

VCOs based on a resonant circuit (such as an LC tank or quartz crystal) are known to have excellent jitter performance [18, 19, 56, 64]. Analysis of noise in resonant-based VCOs is well developed in the literature [22, 30, 32, 57], and design techniques for realizing low jitter performance are relatively well understood.

Unfortunately the requirement of an off-chip tank or crystal defeats the purpose of integrating the PLL function. Actually, integrated inductors have been reported in the GHz frequency range [61]. Unfortunately these have low Q (of order 10) due to resistive losses, and in any case are not practical in the 100MHz to 1GHz frequency range.

### 1.3.2 Multivibrator

A multivibrator VCO can be fully integrable. Much work on multivibrator VCOs has concentrated on their potential for excellent linearity [29, 44, 73, 87, 88], which is an important requirement when the PLL is being used for measurement or to demodulate a PM or FM signal. However, linearity is not as critical a requirement in clock recovery.

Fully integrated clock recovery PLLs have been described using multivibrator VCOs [20, 41, 42, 70, 75]. Unfortunately, despite their excellent linearity, the jitter performance of multivibrators is known to be worse than harmonic oscillators. The literature contains some analysis of jitter in multivibrators [1, 77, 85], and some design techniques for improving jitter are available [74, 84, 86]. Nevertheless, there is a need for improvement of jitter beyond the best achieved by multivibrator VCOs

### 1.3.3 Ring oscillator

Voltage controlled ring oscillators have recently been explored as an alternative to the multivibrator for fully integrated, lower jitter clock recovery PLLs [5, 6, 13-15, 23, 24, 38, 45, 69, 89, 92]. Like the multivibrator, a ring oscillator is fully integrable. In addition, some of the empirical results show promise of excellent jitter performance [45]. These results, however, seem to have been achieved on an isolated, "cut-and-try" basis. There appears to have been no attempt to make a general understanding of jitter in ring VCOs. Indeed, a survey of the literature shows no theoretical analysis of jitter in rings, and thus no techniques for designing to achieve lower jitter in a ring oscillator.

# 1.3.4 Summary: Focus on ring oscillator design techniques

This thesis will focus on techniques for designing ring oscillators to achieve a desired (low) jitter. In particular, this thesis will address design questions such as:

- How is jitter affected by the number of delay stages in the ring? That is, at a given frequency, which is better for low jitter: many fast delay stages, or fewer slow delay stages?

- Within the delay stage itself, what affects jitter? That is, how should circuit parameters (such as bias currents, resistor values, etc.) be chosen to achieve a given desired jitter?

- What are the fundamental limits on jitter that can be achieved? That is, is there any simple relationship between jitter and system-level considerations such as power dissipation or complexity?

### 1.4 How to measure phase

We cannot measure phase directly; we can only observe a signal (usually voltage) which is a function of phase. This section introduces different ways of characterizing phase noise from observations of the voltage. Sections 1.4.1 through 1.4.4 give a qualitative introduction to various jitter and phase noise measurements in the time and frequency domains. A subset of these measurements will be developed more rigorously in Section 1.5.

$\sigma_{x}$  is an advantageous figure-of-merit from the end user's point of view, since it "compresses" all information about jitter performance of the PLL into one (time domain) number. For the PLL designer, however, this compression is a disadvantage, since it obscures information about how to improve jitter performance. Fortunately for the designer, other measurement techniques can be used to characterize jitter in the time domain. Jitter can also be characterized and measured in the frequency domain, which is more appropriate for some applications and design tasks.

A design technique for low jitter PLLs should allow the designer flexibility to work in whatever domain (time or frequency) that gives the most insight into jitter performance. At the same time, the designer must always be able to relate jitter measures in different domains to the end user figure-of-merit,  $\sigma_x$ .

The remainder of this section describes general measurement techniques for characterizing jitter in the time and frequency domains. The goal is to use techniques that require only simple, widely available test equipment.

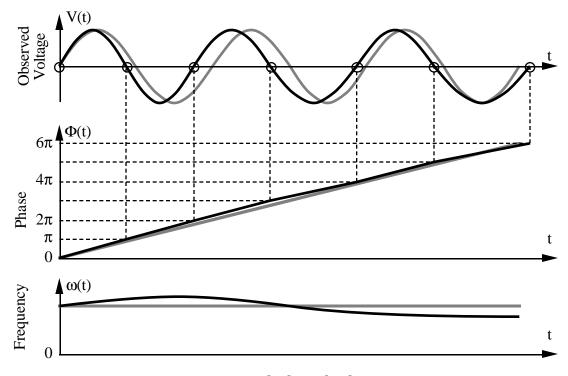

# 1.4.1 Phase measures in time and frequency domains

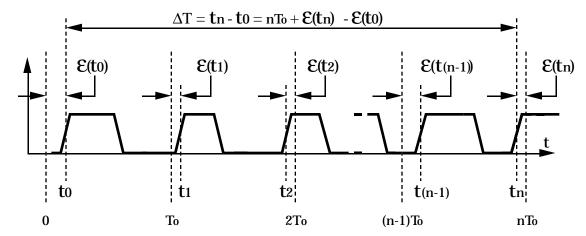

Although phase is a continuous time variable, it is often more convenient to measure it using a sampling approach: that is, to record the times when the phase of the waveform equals a known value. For example, as shown in Figure 1.11, when the voltage waveform crosses zero in a positive going direction we know the phase is a multiple of  $2\pi$ . When there is no phase noise, frequency is constant, phase increases uniformly, and the zero crossing times are evenly spaced at intervals of the period  $T_0 = 1/f_0$ .

In the presence of phase noise, as shown in Figure 1.12, the zero crossing times are not evenly spaced. We can characterize the phase noise by whatever is the most convenient of any of the following equivalent measures:

- variations in periods (frequency) from the ideal constant

- variations in phase from the ideal ramp

- variations in the zero crossing times from the ideal uniform series

Jitter can also be characterized in the frequency domain by the magnitude of sidebands of power spectrum near the "carrier" (center frequency) [66]. The frequency domain approach is the traditional one for measuring phase noise in a clock stability context [22, 67, 83, 100]. Although the PLL's performance is not directly specified in the frequency domain, understanding the frequency domain performance is important as guide to design for improved jitter. This is because, as mentioned in Section 1.2.2, the frequency response of the PLL loop filter shapes the open-loop phase spectrum of the VCO and determines the jitter of the recovered clock under closed-loop conditions.

Figure 1.11. Ideal clock.

Figure 1.12. Clock with phase noise.

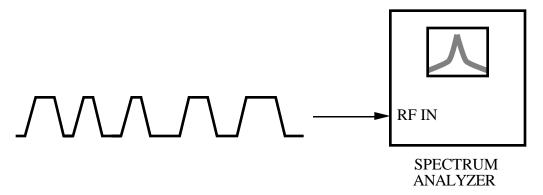

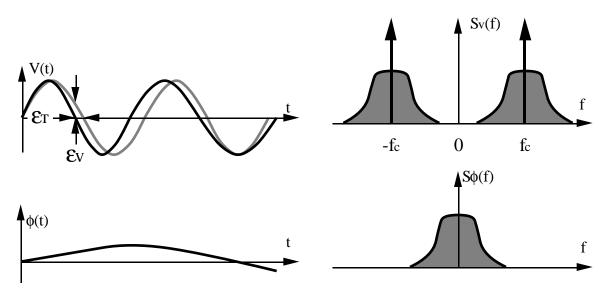

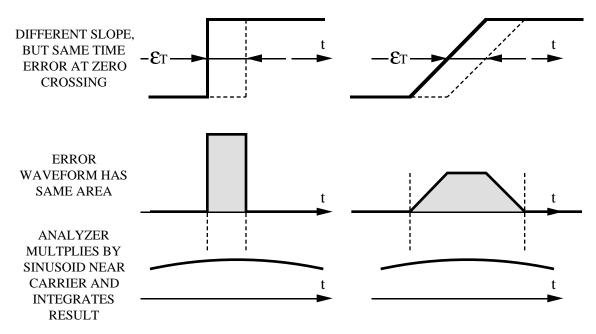

The phase noise power spectral density  $S_{\varphi}(f)$  is measured in the frequency domain using a spectrum analyzer or, for higher accuracy, a more expensive phase noise measurement system [97]. The measurement technique, shown in Figure 1.13, is straightforward: simply feed the clock into the spectrum analyzer. Appendix B shows that the resulting spectrum, if normalized to the carrier power, is equal to the spectrum  $S_{\varphi}(f)$  of the phase jitter process.

Figure 1.13. "Direct spectrum" measurement of phase noise.

### 1.4.2 Time domain: Two sample standard deviation

Most types of jitter can be characterized in the time domain by a two-sample standard deviation. This measurement can be made simply and accurately using a communications signal analyzer (CSA) [96]. This instrument measures the distribution of times between the threshold crossings of trigger and clock waveforms. This measurement can also be made, with more difficulty and less accuracy, by an oscilloscope with a delaying time base [33].

Figure 1.14. Jitter measurement over time delay  $\Delta T$ .

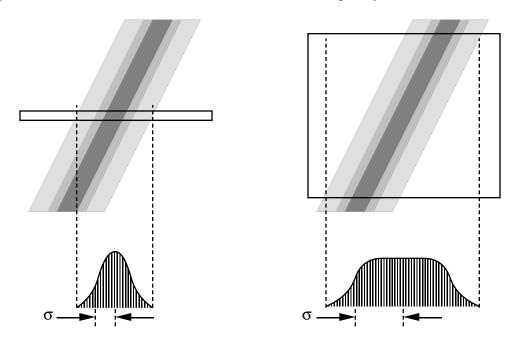

Figure 1.14 shows the idea behind this method of measuring jitter. Input and trigger waveforms  $V_{in}$  and  $V_{trig}$  are applied to the CSA. A time "window" is defined at a delay  $\Delta T$  after the triggering transition of  $V_{trig}$ . The CSA then compiles a histogram of threshold crossings of  $V_{in}$  that occur during this window. The standard deviation  $\sigma$  of this histogram is the result.

This two-sample standard deviation is used as the time domain jitter measure in this thesis. Different measures are obtained when different signals from the PLL are used for  $V_{in}$  and  $V_{trig}$ , with the PLL operating under different conditions.

# Conditions for validity

Compiling this histogram takes a finite amount of time, usually of order seconds. If there is any drift in frequency during this time, (for example, due to thermal effects), then  $\sigma$  is not defined [67] and any attempt to measure a two-sample standard deviation will diverge. Drift is reduced by allowing sufficient time for device warm-up and thermal stabilization.

The CSA's internal time base is the reference which defines the interval  $\Delta T$ . Therefore the jitter of this time base must be better than the clock under test. In practice, this is not a problem except at very long  $\Delta T$  delays.

#### 1.4.3 Other time domain measures

A disadvantage of the two sample standard deviation is that  $\sigma$  does not converge in the presence of nonstationary noise processes with frequency characteristic 1/fn when n>2 [22]. This is most often a problem when long term frequency drift is present. For this reason a more robust statistic, called the Allan variance, has been developed [2]. There is an extensive literature relating the Allan variance to frequency domain performance.

A disadvantage of the Allan variance is that it requires at least three correlated time measurements and cannot be performed with the CSA. This conflicts with our goal of using only simple, commonly available test equipment. Therefore the Allan variance will not be used in this work.

There are many other less common time domain jitter measures that have been developed [52]. In general, like the Allan variance, these are more robust but require more complicated measurement instrumentation. For the purposes of this thesis the two-sample standard deviation is sufficiently robust and has the advantage of being reasonably simple to measure.

# 1.4.4 Frequency domain phase measures

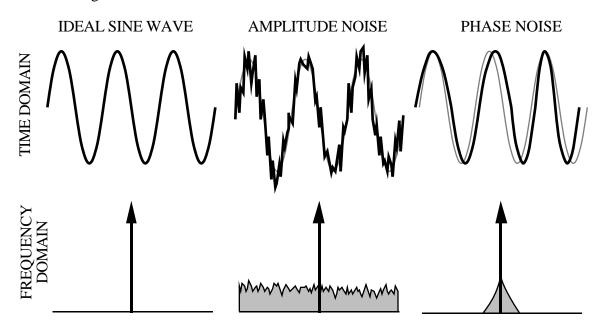

Phase noise can also be characterized in the frequency domain. An ideal sine wave in the time domain corresponds to an ideal impulse in the (single sided) frequency domain, as shown in Figure 1.15.

Figure 1.15. Clock jitter in time and frequency domains.

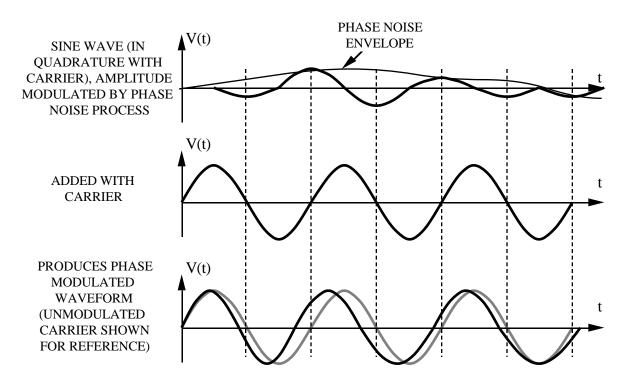

Consider the spectrum of an ideal sine wave with additive white noise, shown in Figure 1.15. The noise adds uncertainty to our measurement of the zero crossings of the waveform. We can imagine "cleaning up" the waveform with a bandpass filter. However, we will still have noise near the carrier. We can characterize the phase noise by the size and shape of the "close in" sidebands around the ideal impulse in frequency.

Actually, care must be taken in interpreting a spectrum. A magnitude spectrum "hides" information since there is no way to distinguish phase noise power from amplitude noise power. In practice, some form of limiting is used to remove amplitude fluctuations [66]. This ensures that only phase noise power is present in the waveform.

# Conditions for validity

The phase noise of the spectrum analyzer's internal reference oscillator must be better than the oscillator under test. In practice, at the small offset frequencies where phase noise is measured, most spectrum analyzers have lower phase noise than multivibrator and ring oscillators.

Some spectrum analyzers may require a calibration factor when measuring the power density of noise (as opposed to spectral lines). This is because most spectrum analyzers measure amplitude with an envelope detector, which has different response to noise than to a pure spectral tone [99]. Some analyzers (such as the HP4195A [98]) automatically add the calibration factor when the display is set to units of noise density.

### **1.4.5 Summary**

We cannot observe phase directly, but there are several ways of measuring phase and phase errors from an observable signal. These techniques can help the designer improve jitter by providing more information than the figure-of-merit  $\sigma_x$ . The general measures that will be addressed in this thesis are the two-sample standard deviation in the time domain, and the phase noise power spectral density in the frequency domain. Both of these measurements can be made in a straightforward fashion with commonly available telecommunications test equipment, an important point for the practicing designer.

### 1.5 Measures that will be related in this thesis

In addition to the time or frequency domain options for measurement, jitter can also be measured with the PLL open or closed loop. Figure 1.26 summarizes five different measurement techniques, all of which will be related to one another by this work. Following is a more detailed discussion of each of these techniques and their advantages and disadvantages.

# 1.5.1 Case (i): Frequency domain, VCO open loop

# Measurement Technique

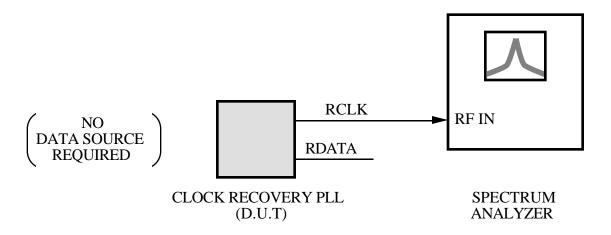

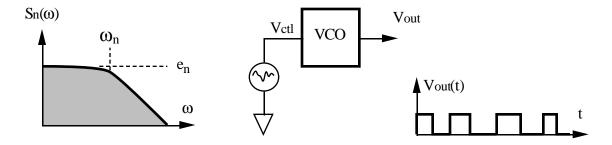

The open loop VCO spectrum is measured as shown in Figure 1.16. The free-running VCO output is applied to the spectrum analyzer input. The resulting spectrum, normalized to the carrier power, is  $S_{\phi OL}(f)$ .

### Result

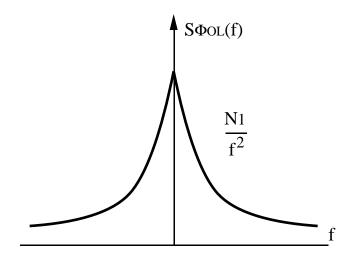

With the VCO operating open loop,  $S_{\varphi OL}(f)$  as measured on the spectrum analyzer has the characteristic shown in Figure 1.17. Since the VCO integrates phase noise, the noise power increases as  $1/f^2$ , where f is the offset from the center frequency. We can fit the measurement to a characteristic

$$S_{\phi OL}(f) = \frac{N_1}{f^2} \tag{1-9}$$

to define a frequency domain figure of merit N<sub>1</sub>.

# **Advantage**

This is a simple, quick test to obtain frequency domain figure of merit N<sub>1</sub>.

# Disadvantage

It is not immediately apparent that the frequency domain figure of merit  $N_1$  is related to our ultimate design goal: the end user's time domain figure of merit  $\sigma_x$ .

Figure 1.16. Measurement technique: Frequency domain, open loop.

Figure 1.17. Measurement result: Frequency domain, open loop.

# 1.5.2 Case (ii): Frequency domain, PLL closed loop

# Measurement Technique

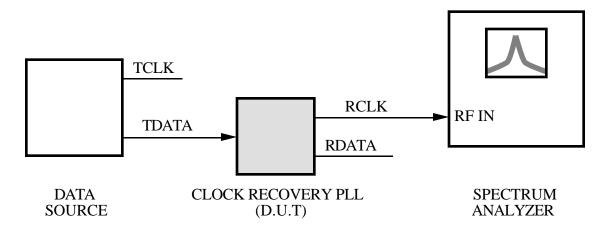

The closed loop VCO spectrum is measured as shown in Figure 1.18. The PLL is locked to a data source; the VCO output is applied to the spectrum analyzer input. The resulting spectrum, normalized to the carrier power, is  $S_{\Phi CL}(f)$ .

#### Result

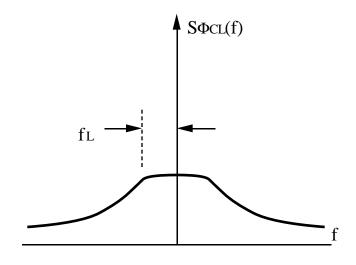

When the loop is closed around the VCO,  $S_{\varphi CL}(f)$  is given by the sum of jitter contributions from the transmit clock and the VCO, as shaped by loop filter. Assuming that the jitter of the transmit clock is negligible, the VCO will be the dominant contributor of phase noise at all offset frequencies [65].  $S_{\varphi CL}(f)$  will have the characteristic shown in Figure 1.19. This is simply the closed loop phase noise power spectrum of Figure 1.10 translated to the carrier frequency. Since the PLL loop drives the VCO to track the transmit clock, the noise power levels off at offset frequencies below the loop bandwidth. As shown in Figure 1.10, the leveling off is due to the noise p.s.d. rolling up at the same rate as the noise transfer function rolls down.

### Advantage

The effect of loop bandwidth on jitter in readily apparent in the frequency domain.

# Disadvantage

The spectrum is not directly indicative of end user's time domain figure of merit  $\sigma_x$ .

Figure 1.18. Measurement technique: Frequency domain, closed loop.

Figure 1.19. Measurement result: Frequency domain, closed loop.

# 1.5.3 Case (iii): Time domain, closed loop, transmit clock referenced

### Measurement technique

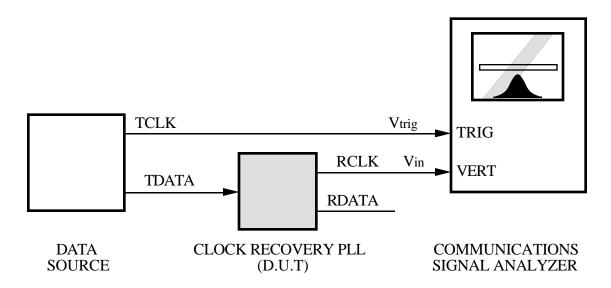

This measurement is made as shown in Figure 1.20. The transmit clock TCLK is used as the CSA trigger  $V_{trig}$ ; the recovered clock RCLK is observed as the CSA input  $V_{in}$ . In the presence of jitter, a distribution of threshold crossing times is observed. The CSA records a histogram of this distribution as shown in Figure 1.21.

### Result

The standard deviation of the distribution of threshold crossing times of RCLK, referenced to TCLK, is  $\sigma_x$ .

# **Advantage**

This measurement gives the end user's figure of merit  $\sigma_x$ . This test is a simple, quick indicator of how well the PLL performs the clock recovery function.

# Disadvantage

This test requires that the transmit clock be available at the receive end of the link. While this is not a problem in a laboratory test, in the field the transmit clock may be at the other end of several kilometers of optical fiber.

This test also requires the PLL to be operating closed loop. VCO design and simulation would be simplified if we could consider the VCO by itself (open loop), while being able to predict the closed loop  $\sigma_x$ .

While this test has the advantage of being simple and quick, it provides little information on improving jitter if  $\sigma_x$  is not satisfactory.

Figure 1.20. Measurement technique: Time domain, closed loop, transmit clock referenced.

Figure 1.21. Measurement result: Time domain, closed loop, transmit clock referenced.

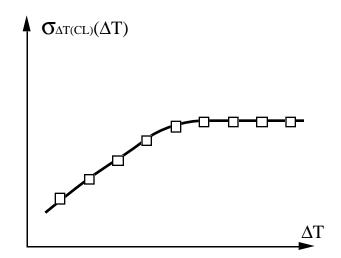

# 1.5.4 Case (iv): Time domain, closed loop, self referenced

### Measurement technique

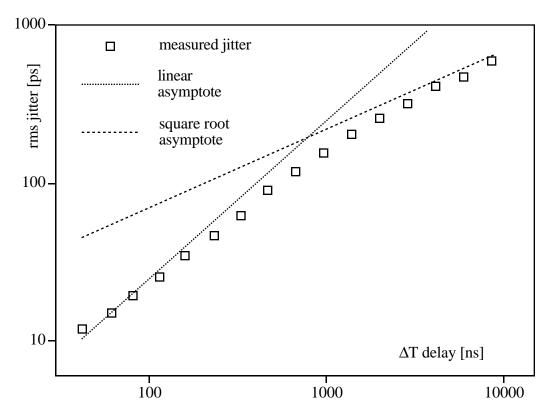

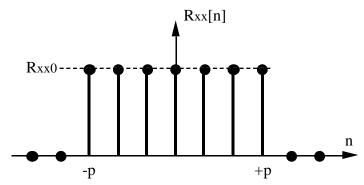

This measurement is made as shown in Figure 1.22. The recovered clock is used as both the trigger and the input to the CSA. The CSA compares the phase difference between transitions in the clock waveform, separated by a delay  $\Delta T$  derived from the CSA's internal time base. As in the previous case, a distribution of threshold crossing times is observed.

### Result

In this measurement technique, however, the standard deviation  $\sigma_{\Delta T}$  from the mean phase is observed to depend on the delay  $\Delta T$ . The standard deviations  $\sigma_{\Delta T(CL)}(\Delta T)$  can be plotted as a function of delay  $\Delta T$ ; a plot of the form as shown in Figure 1.23 results. Note that, unless otherwise specified, all time domain jitter plots in this thesis are on log-log axes. Jitter may be quantified by the standard deviation at one delay, or more completely by the functional relationship between  $\sigma_{\Delta T(CL)}$  and  $\Delta T$ .

# **Advantage**

This measurement requires access only to the recovered clock and thus can be made even if the transmit clock is inaccessible. Also, the plot of  $\sigma_{\Delta T(CL)}$  vs.  $\Delta T$  provides more information than the single number  $\sigma_x$ .

### **Disadvantages**

This test requires the PLL to be operating closed loop. Also, the accuracy of the  $\sigma_{\Delta T(CL)}$  vs.  $\Delta T$  plot may be degraded by the jitter of the CSA time base, especially for large  $\Delta T$ .

Figure 1.22. Measurement technique: Time domain, closed loop, self referenced.

Figure 1.23. Measurement result: Time domain, closed loop, self referenced.

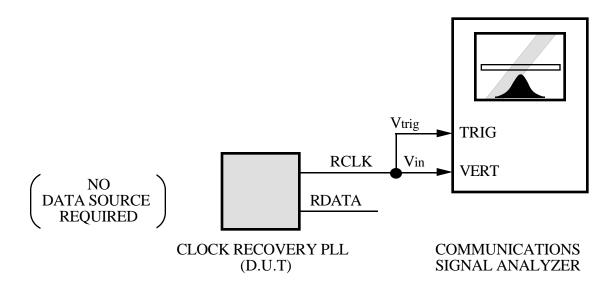

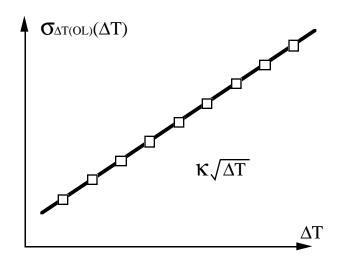

# 1.5.5 Case (v): Time domain, open loop, self referenced

### Measurement technique

This measurement is made as shown in Figure 1.24. The test is similar to that shown in Figure 1.22, except that the PLL loop is opened so that the VCO free runs.

#### Result

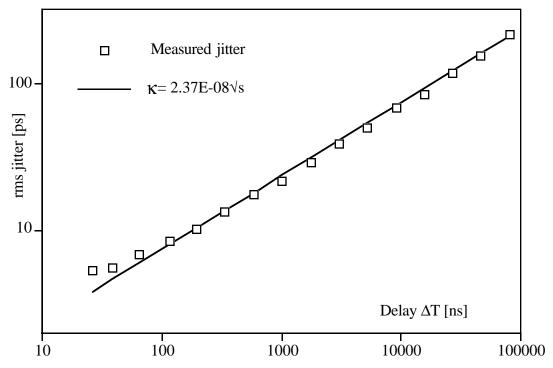

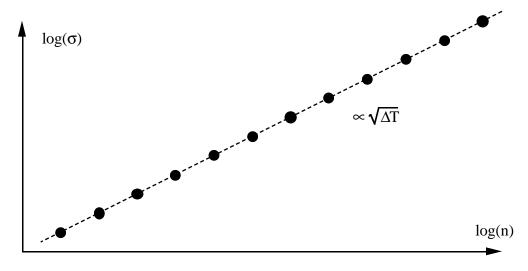

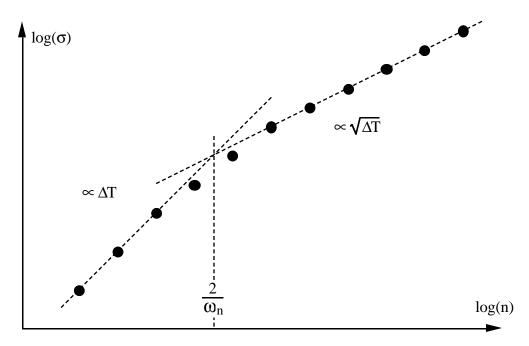

Again, the standard deviations  $\sigma_{\Delta T(OL)}(\Delta T)$  are plotted as a function of delay  $\Delta T$ ; in this case a plot of the form as shown in Figure 1.25 results. We will see that, for a process that can be approximated in the frequency domain by equation (1-9), the plot of  $\sigma_{\Delta T(OL)}(\Delta T)$  vs.  $\Delta T$  will take the form

$$\sigma_{\Delta T(OL)}(\Delta T) \approx \mathbf{K} \sqrt{\Delta T}$$

(1-10)

where the proportionality factor K is a time domain figure of merit.

# **Advantages**

No transmit clock or data source is required. The VCO can be measured and analyzed in isolation. Again the plot of  $\sigma_{\Delta T(OL)}(\Delta T)$  vs.  $\Delta T$  provides more information than the single number  $\sigma_x$ .

### **Disadvantages**

It is not immediately apparent that the time domain figure of merit K is related to the end user's time domain figure of merit  $\sigma_x$ . Also, as in Section 1.5.4, accuracy is limited by the jitter of the CSA time base for large  $\Delta T$ .

Figure 1.24. Measurement technique: Time domain, open loop, self referenced.

Figure 1.25. Measurement result: Time domain, open loop, self referenced.

# **1.5.6 Summary**

Five techniques are presented for measuring VCO contribution to PLL jitter, each with its own advantages and disadvantages. Figure 1.26 summarizes these techniques. In general, open loop measures have the advantages of being simpler and more relevant to the task of stand-alone VCO design, but have the disadvantage of being apparently unrelated to the end user's figure-of-merit  $\sigma_x$ . In general, closed loop measures have the advantage of being closely related to  $\sigma_x$ , but have the disadvantage of forcing the designer to consider the entire PLL rather than focusing only on stand-alone VCO design.

Figure 1.26. Summary of jitter measurement techniques.

### 1.6 Motivation and goals of this work

There are many applications for low jitter, PLL-based clock recovery. Fully integrated PLLs have a substantial cost and size advantage over PLLs requiring off-chip resonant elements. Ring oscillators have shown promise in low jitter applications, but there are no tools available to predict and design for jitter in ring oscillators.

### **1.6.1** Goals

Thus the primary goal of this thesis:

# Develop design tools for ring VCO jitter

These tools would answer design questions posed in Section 1.3.4 regarding ring architecture, circuit design, and fundamental limits on jitter.

To ease design, the tools should also allow flexibility to work in whichever domain of Figure 1.26 gives the most insight, while relating to the final figure of merit  $\sigma_x$ . For example, although  $\sigma_x$  is defined in the time domain, insight for guiding some design decisions (e.g., effects of the loop filter and aliasing of noise sources [11, 86]) is more apparent in the frequency domain.

A secondary related goal is:

# Simulation of PLL jitter

Once we have a tentative design, it is desirable to have a simulation tool to verify that design before going to the expense of fabricating silicon. Although we have modeled the PLL as a linear system, the VCO itself is a nonlinear circuit. Meaningful jitter simulation requires transient analysis with explicit noise sources [10]. Such a simulation is intractable with the full PLL circuit but is possible for the open loop VCO. Again, this requires relating performance measures from the different domains of Figure 1.26.

Achieving these goals requires:

# Technique for relating time / frequency, open / closed loop jitter measures

A technique for relating jitter measures from the various domains identified in Figure 1.26 enables simplified design and simulation of a low jitter VCO. The difficulty is that design and simulation are easiest on the stand-alone, open loop VCO - where nonstationary noise precludes the use of transform tools to move between the time and frequency domains. The ultimate concern is the jitter of the closed loop PLL system. With this time/frequency technique the designer can work in whatever domain is easiest while still being able to accurately predict performance when measured by the end user.

### 1.6.2 Other benefits

Although the techniques in this thesis are developed for PLL ring VCO design, they are applicable to any oscillator with a  $1/f^2$  p.s.d. This will be demonstrated in Chapter 4 where the time/frequency technique of Chapter 2 is applied to a harmonic oscillator spectrum and gives the same result as previous analysis.

This work also aids evaluation of actual devices. For example, in the AD802 we can open the PLL loop, set the VCO to a fixed frequency, and measure the stand alone, open loop VCO performance. From this measurement we can predict what the closed loop performance should be if limited only by the VCO jitter. Then we can compare this prediction with actual measurements to determine if other components (such as the phase detector or loop filter) are degrading the closed loop performance.

# **1.6.3 Summary**

Chapter 2 will develop the time/frequency, open/closed loop jitter technique. In Chapters 4-6, the technique is used to develop design tools for ring VCOs at various levels of detail. The applications of these principles to simulation is implicit in the results presented in Chapters 4-6, as well as in Appendix I.

### 2. Technique for relating time / frequency domain jitter measures

### 2.1 Theoretical development

The contribution of this chapter is a mathematical technique for linking all of the performance measures shown in Figure 1.26. Note that the performance measures in the "open loop" portion of the figure correspond to nonstationary phase noise processes. This is shown in the unbounded standard deviation as delay time goes to infinity in Figure 1.25, and the nonconvergent noise power integral as offset frequency goes to zero in Figure 1.17.

Following is the derivation of these mathematical relationships.

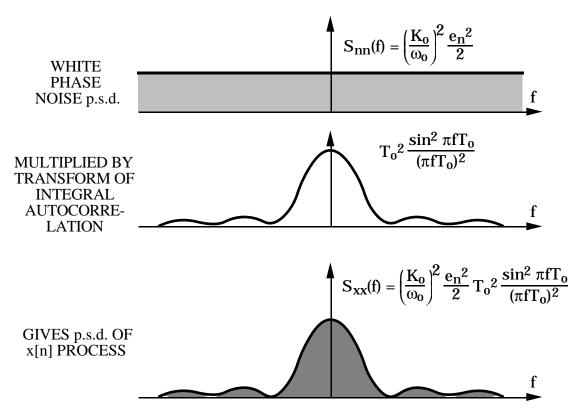

### 2.1.1 Case (i): Frequency domain, VCO open loop

When the PLL loop is opened and the VCO is free running, we assume the phase noise power spectral density to be dominated by integrated white noise. With this assumption, the p.s.d.  $S_{\Phi OL}(f)$  at the VCO output can be modeled by

$$S_{\phi OL}(f) = \frac{N_1}{f^2} \tag{2-1}$$

where f is the offset frequency from the "carrier" (VCO free-running frequency) [66]. The value of N<sub>1</sub> for a particular VCO can be determined from a spectrum analyzer measurement. Since (2-1) goes to infinity as f approaches zero, the integral of phase noise power over all frequencies does not converge. This makes sense intuitively, since the phase error of an open loop oscillator can wander arbitrarily far in its "random walk."

The spectrum analyzer measures in power density in units of [W/Hz]. This must be normalized relative to the carrier power [W], to give  $S_{\varphi OL}(f)$  expressed in units of [rad<sup>2</sup>/Hz] or dBc/Hz (power below carrier). N<sub>1</sub> has dimensions of rad<sup>2</sup>· Hz.

# 2.1.2 Case (ii): Frequency domain, PLL closed loop

From Section 1.2.2 and Figures 1.9 and 1.10, however, we see that the effect of the loop filter is to make the closed loop p.s.d. of the form

$$S_{\phi CL}(f) = \frac{N_1/f_L^2}{1 + (f/f_L)^2}$$

(2-2)

where f<sub>L</sub> is the loop bandwidth, which is known by design.

# 2.1.3 Case (iii): Time domain, closed loop, transmit clock referenced

Under the  $1/f^2$  dominated approximation, with the PLL loop closed, the phase noise process is stationary. Equation (2-2) can be integrated over all frequencies to give the variance (average power) of the jitter process, which gives the end user's measure of jitter performance,  $\sigma_x$ :