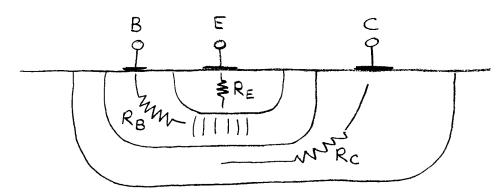

#### BJT "REAL WORLD" PARASITIC R

### EMITTER RE

USUALLY ~15. (E HEAVILY DOPED), NOT A PROBLEM CAUTION: POWER APPLICATIONS!

SOLUTION: LARGER EMITTER AREA LOWERS RE

### COLLECTOR RC

HIGH (C LIGHTLY DOPED) ~ 1kD.

BUT: IN SERIES WITH CURRENT SOURCE (NOISE OK)

CAUTION; QUASISATURATION (ICRC DROP FORWARD

BIAS ON INTERNAL B-C JUNCTION)

SOLUTION: LOWER R. WITH BURIED LAYER

### BASE RB

MODERATE: ~ 1000 TO 1ksl USUALLY MAJOR NOISE OFFENDER AT INPUT; SEES FULL GAIN

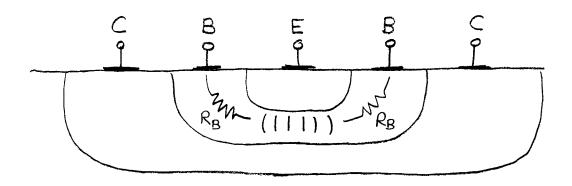

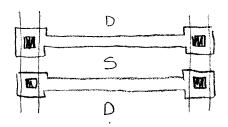

# RB SOLUTION "DOUBLE BASE"

PARALLEL COMBINATION RB/2

BUT: CJC (B-C) INCREASED (LARGER JCT AREA)

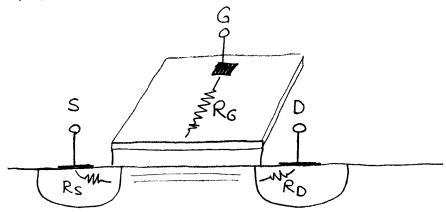

MOSFET "REAL WORLD" PARASITIC R

## $R_S, R_D$

USUALLY ~ 10 TO 100 D (S,D HEAVILY DOPED)

PLUS CONTACT RESISTANCE

CAUTION: POWER APPLICATIONS!

SOLUTION: LOTS OF CONTACTS

## RG GATE POLY RESISTANCE

CAN BE MODERATE TO HIGH (GATE GEOMETRY) USUALLY MAJOR NOISE OFFENDER

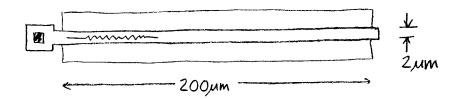

# EXAMPLE: W/L = 200/2 IN 2000/11 POLY

TO CENTER (AVERAGE)

$$R_G = \left(\frac{100\mu\text{m}}{2\mu\text{m}}\right)(20\Omega/0) = 1 \text{ k}\Omega$$

#### SOLUTIONS

PROCESS: SILICIDE GATE

LOWERS SHEET R BY ~ 10X

LAYOUT: FINGERS; DOUBLE CONTACT

WIN BY N2 FOR N FINGERS RG, N IN PARALLEL