### **Background**

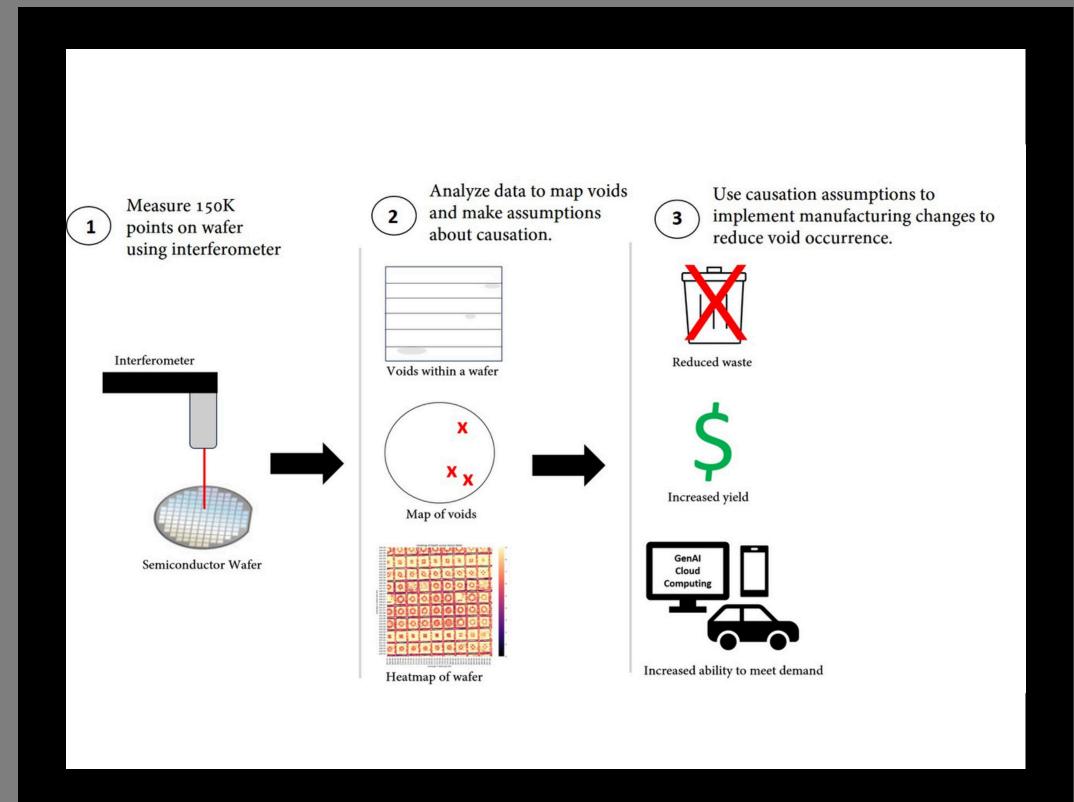

This study explores the use of low-coherence interferometry as a means for identifying voids in semiconductors and their effects based on size, location, and the manufacturing step in which they are introduced. In high-volume semiconductor manufacturing, voids (small defects) can affect the semiconductor in a variety of ways, from intermittent malfunctions to complete failure, resulting in lower yields. Past studies have looked at specific causations, such as a void's proximity to bond balls, but little has been published about the general features and causation of voids in relation to their impact. Our study will use IR measurements to map voids and the correlation of the voids' size and locations will be used to identify void causation. Identifying a low-cost method that can be used to identify void causation will enable the semiconductor industry to improve its manufacturing processes and reduce yield loss due to voids. This is important to the industry, as semiconductors power the world's technologies, from cars to smartphones, and the need for semiconductor chips continues to rise with the increasing demand to support generative AI computing.

# Methodology

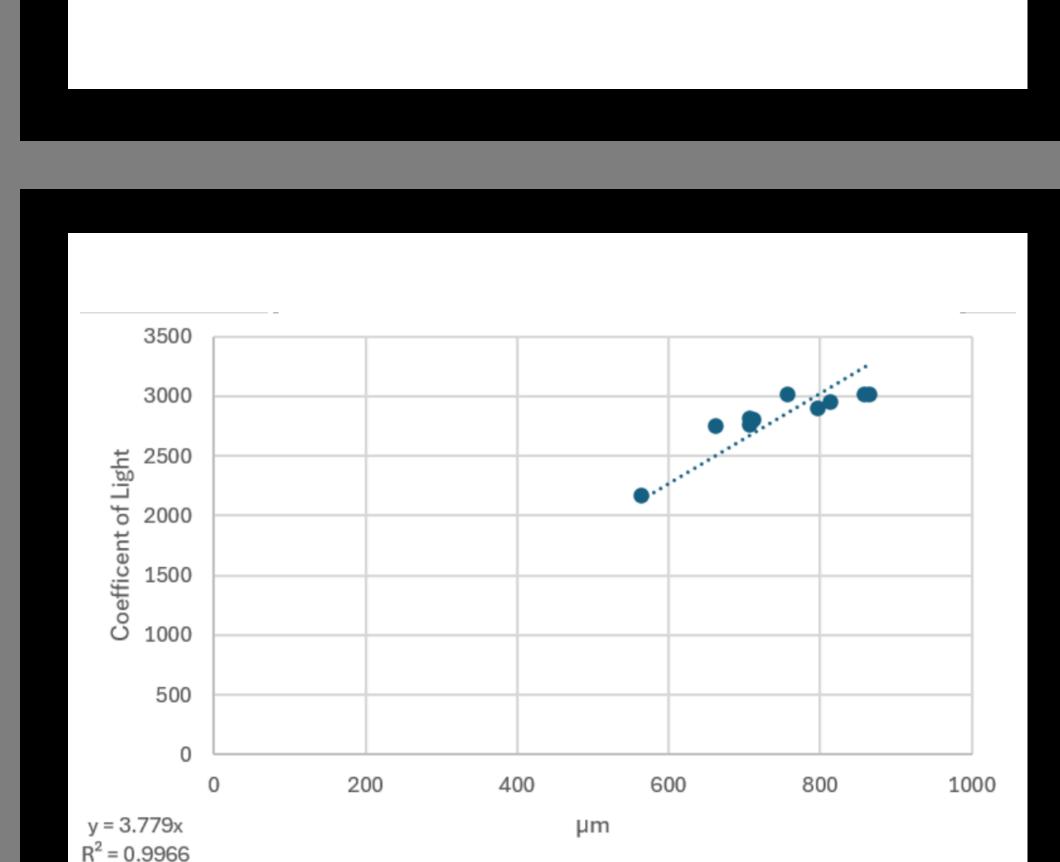

The start of this project is attempting to prove the accuracy of Infrared interferometry. By measuring calibration discs, which are small discs that are premade to have an exact thickness in nanometers. With this info we will scan these calibration discs then find the thickness that we receive and compare it to the given thickness that they are supposed to be. Since the infrared interferometry will return the coefficient of light as the form of measurement instead of the thickness in nanometers, we can make a line of best fit and see if the R^2 value supports our claim that this is an accurate form of measurement. Then we will use 30 semiconductors that would have been disposed of due to failing a void check within the semiconductor manufacturing process and use Infrared interferometry to see the exact location and size of the voids. Then we will be able to study what factors affect if voids are fatal to a semiconductor. Then supply semiconductor manufacturers with this data that should allow for them too improve the semiconductor manufacturing process.

# Identifying the Causation of Voids within Semiconductors to Reduce Waste and Increase Yield

By: Danny Harn

### **Engineering Goal**

Semiconductors are critical to the world's technologies, from cars to smartphones, and the need for semiconductor chips continues to rise with the increasing demand to support generative AI computing.

Semiconductor manufacturers must ensure the highest yield possible, but today are challenged by voids (small defects) introduced during the manufacturing process. These voids can have various effects on a semiconductor, from intermittent malfunction to complete failure, but it is unknown why different types of voids have varying effects. It is also not clear why voids occur during specific steps in the process. These two gaps in knowledge can make it extremely difficult to develop and implement void mitigation strategies in the semiconductor manufacturing process.

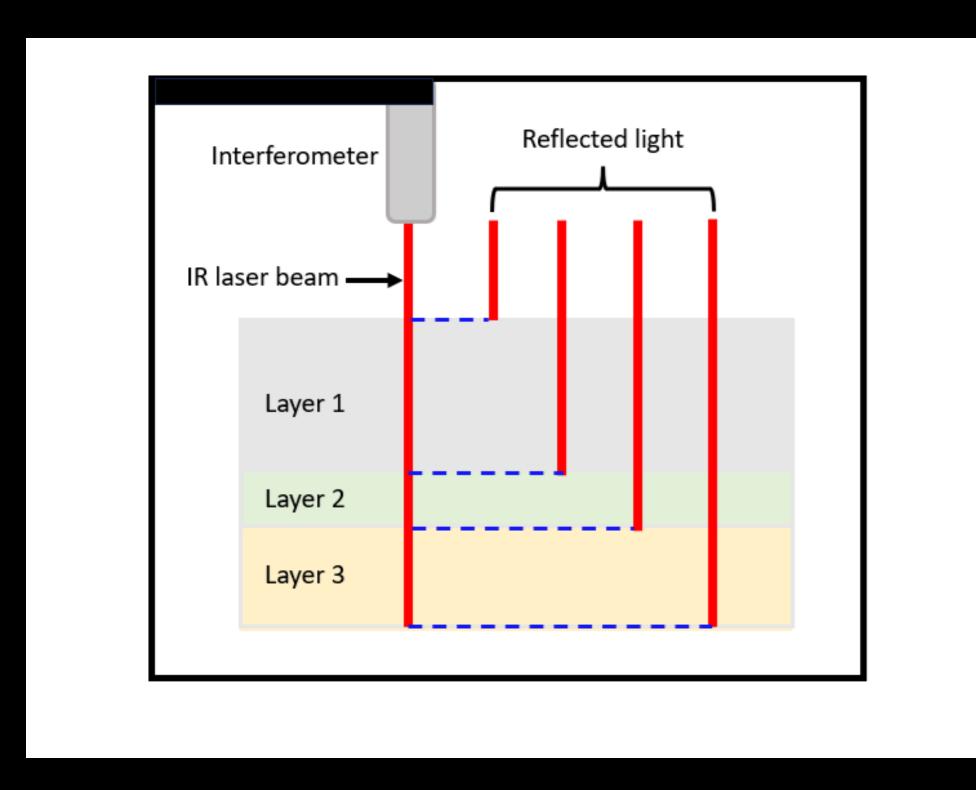

# What is Infrared interferometry?

Infrared interferometry is a form of measurement using an infrared laser. So, a laser is shot down at what you are trying to measure and mattering by the amount light return you can make a measurement. This is extremely accurate being able to measure in nanometers which is a millionth of a meter. With this we can use it on a semiconductor as their will be different thickness's within a semiconductor when a void is present. As the small air pocket will display a different value as the light traveling through the small air pocket will lead to a different amount of light loss. This is perfect for this project as we are attempting to find voids within semiconductors and this even has been proven too work in past studies like (Poduje, N., Kerr, W., & Turner, K. T. 2010). So infrared interferometry is a form of metrology that is extremely accurate and is proven method that works for the purposes of this project.

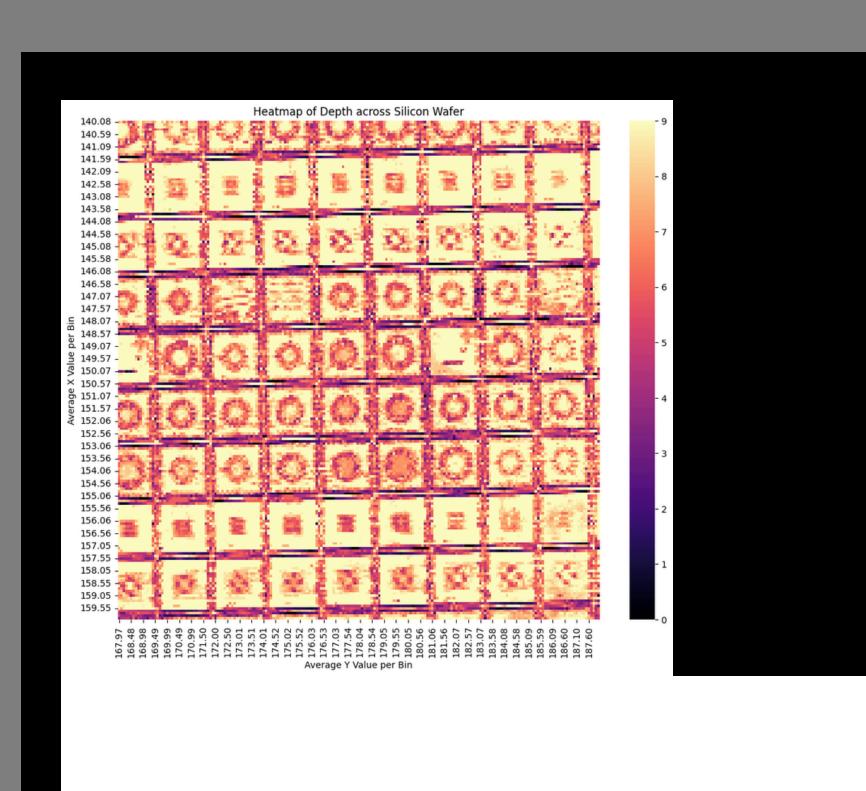

#### **Analysis Of Heatmap**

Needs to be written

#### **Problem Need**

Semiconductors are critical to the world's technologies, from cars to smartphones, and the need for semiconductor chips continues to rise with the increasing demand to support generative AI computing.

Semiconductor manufacturers must ensure the highest yield possible, but today are challenged by voids (small defects) introduced during the manufacturing process. These voids can have various effects on a semiconductor, from intermittent malfunction to complete failure, but it is unknown why different types of voids have varying effects. It is also not clear why voids occur during specific steps in the process. These two gaps in knowledge can make it extremely difficult to develop and implement void mitigation strategies in the semiconductor manufacturing process.

## References

Poduje, N., Kerr, W., & Turner, K. T. (2010). Inspection of Bonded Interfaces Using Scanning Infrared Interferometry. *ECS Transactions*, *33*(4), 537. <a href="https://doi.org/10.1149/1.3483545">https://doi.org/10.1149/1.3483545</a>

Kasaya, K., Yoshikuni, Y., & Ishii, H. (1996). Measurements of a semiconductor waveguide using a low-coherence interferometric reflectometer. *IEEE Photonics Technology Letters*, *8*(2), 251–253. IEEE Photonics Technology Letters. <a href="https://doi.org/10.1109/68.484257">https://doi.org/10.1109/68.484257</a>

Allen, R. A., Rudack, A., Read, D., & Baylies, W. (2010). Intercomparison of Methods for Detecting and Characterizing Voids in Bonded Wafer Pairs. *ECS Transactions*, *33*(4), 581. <a href="https://doi.org/10.1149/1.3483550">https://doi.org/10.1149/1.3483550</a>

Kuo, Y.-L., Lin, Y.-C., Lin, Y.-T., Huan, H.-S., & Su, D. (2004). Failure analysis of IMC cracking and voiding induced by molding compound voids in advanced wire bonding packages. *Proceedings of the 11th International Symposium on the Physical and Failure Analysis of Integrated Circuits. IPFA 2004 (IEEE Cat. No.04TH8743)*, 221–224. <a href="https://doi.org/10.1109/IPFA.2004.1345603">https://doi.org/10.1109/IPFA.2004.1345603</a>

Takahashi, A. & Ishida, Y. (2004). *Method for manufacturing semiconductor device* (Japan Patent Off

Takahashi, A., & Ishida, Y. (2004). *Method for manufacturing semiconductor device* (Japan Patent Office Patent). https://patents.google.com/patent/JP2004311603A/en?oq=JP2004311603A.pdf